Videos

This short SourcePoint video is a supplement to our recent webinar, Debug of Hyper-V, Secure Kernel, VBS Enclaves, Defender, and other Windows secrets. It demonstrates the debug of the Secure Kernel and VBS Enclave code.

To see the full webinar, click on the GoToWebinar registration link here.

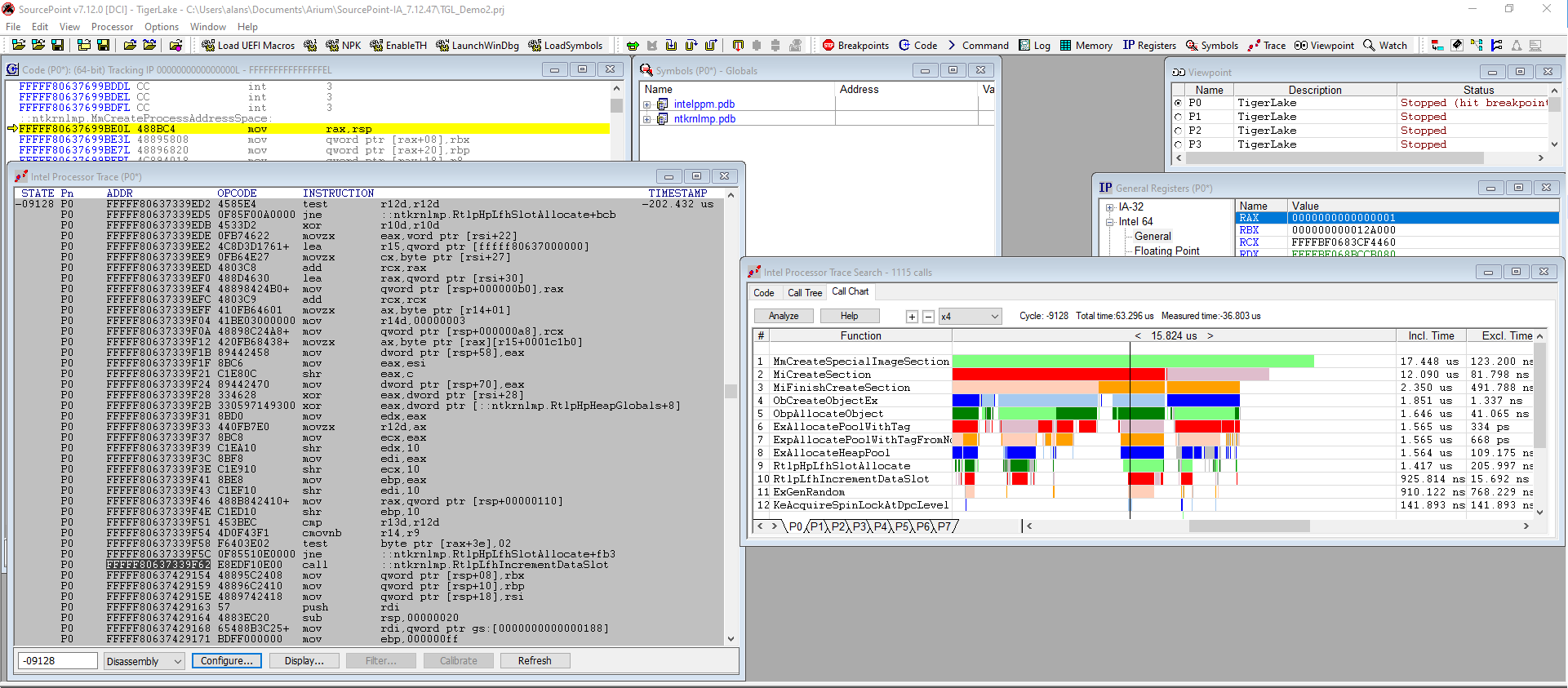

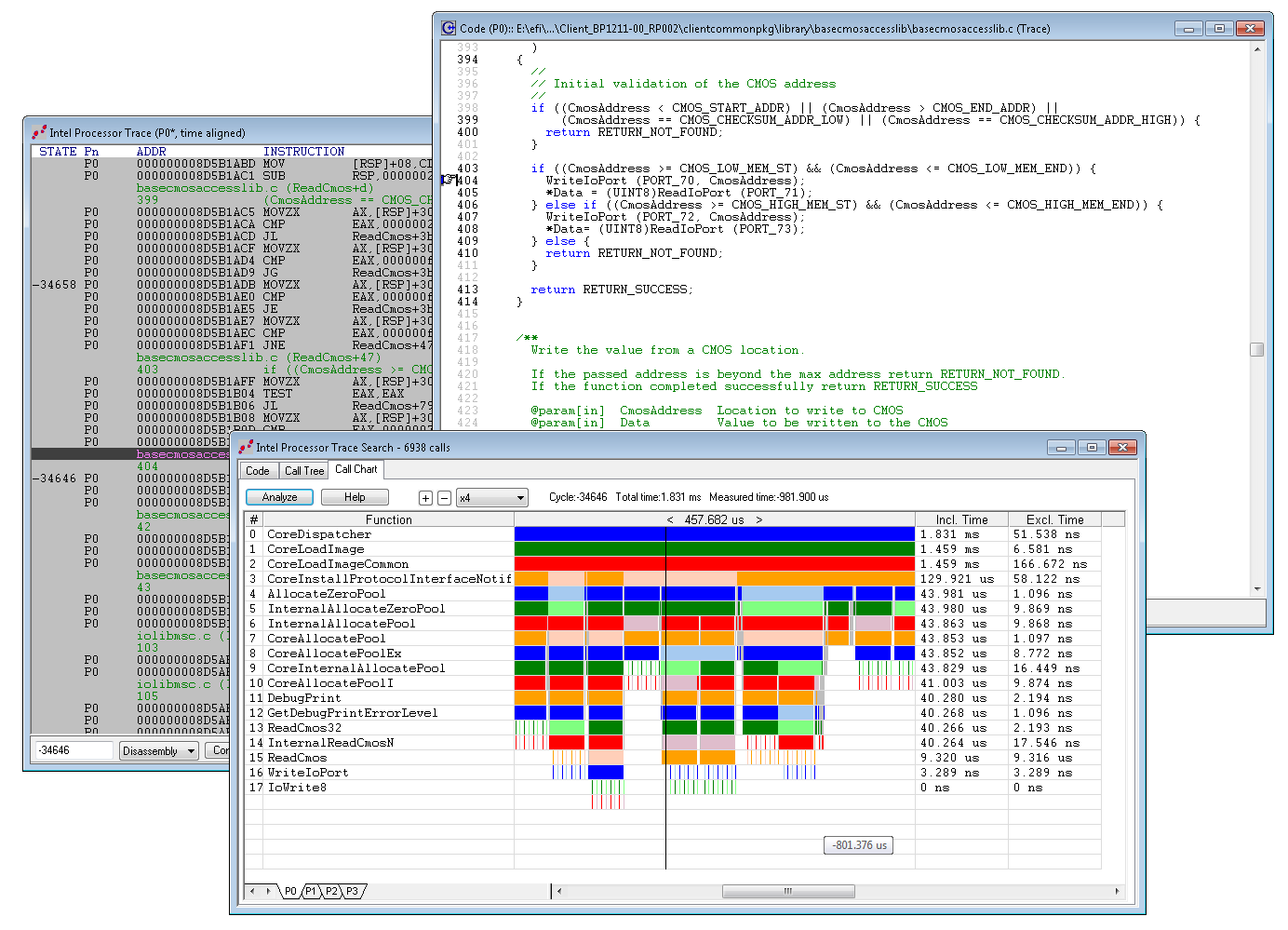

Using SourcePoint’s unique JTAG-based Intel x86 debug capabilities, we take a look at when Hypervisor-managed Linear Address Translation (HLAT), a security feature that precludes non data-driven kernel exploits, is initialized upon Windows boot.

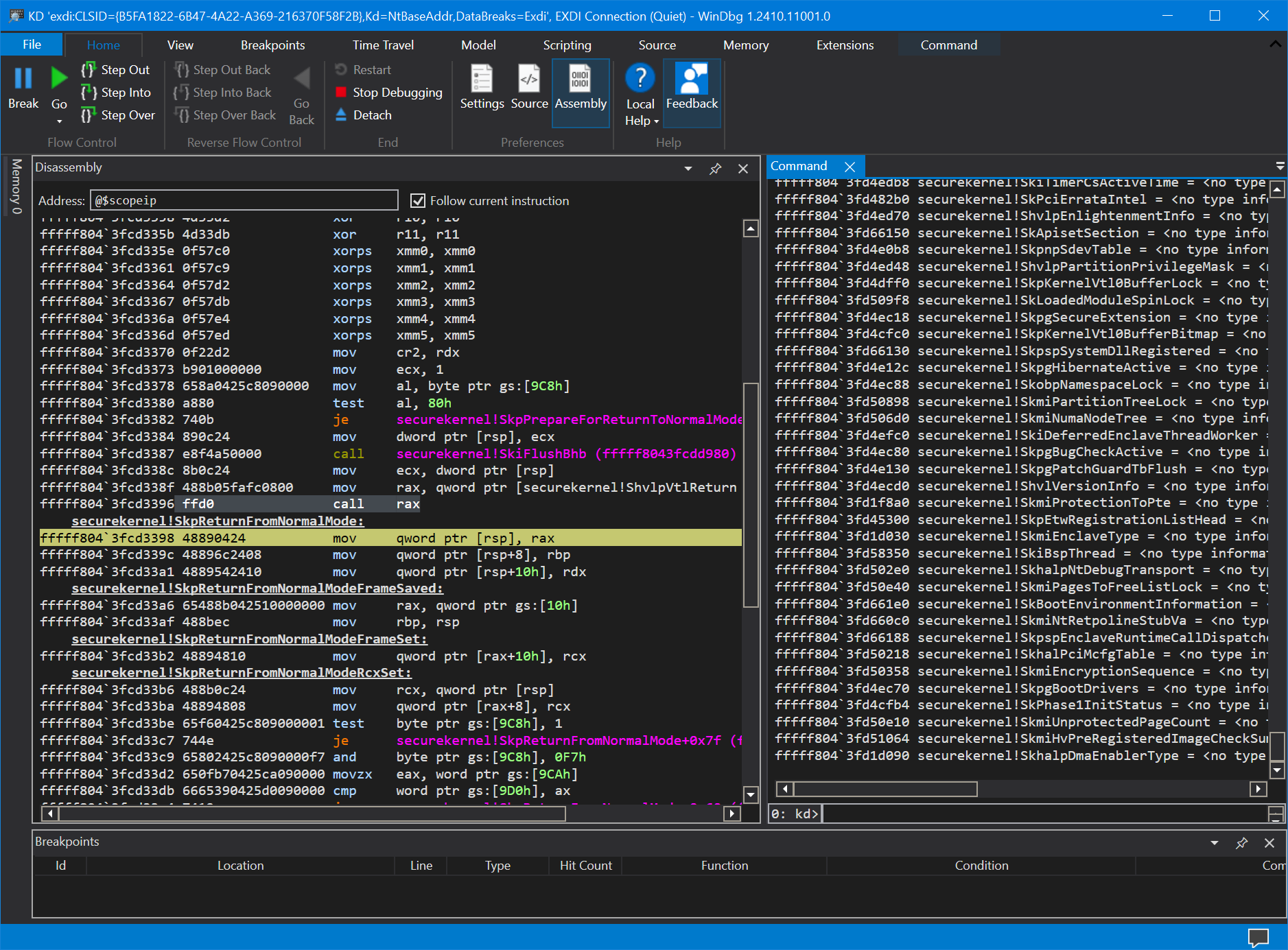

WinDbg is Microsoft’s Windows debugger, and SourcePoint is ASSET’s JTAG-based debugger. Integrate the two over the EXtended Debug Interface (EXDI) and you get the unparalleled capabilities of Intel Processor Trace, Architectural Event Trace, SMM and VMM breakpoints, and others.

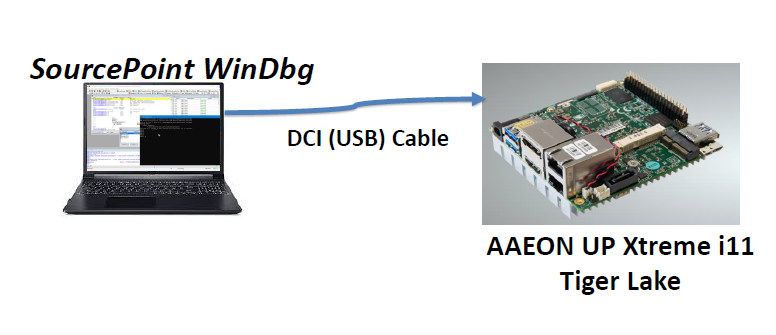

This demonstration shows these disruptive technologies applied to Windows kernel debugging on an AAEON UP Xtreme i11 Tiger Lake board, using the Intel Direct Connect Interface (DCI). The full webinar is available here, but with lower audio quality for the demo section.

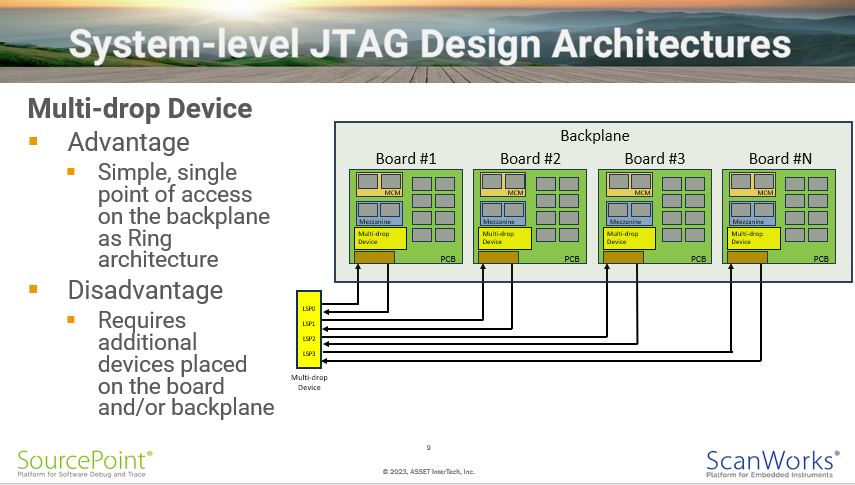

System-level JTAG, or SJTAG, expands the application potential of JTAG significantly beyond the traditional board-level scope of structural test and device programming.

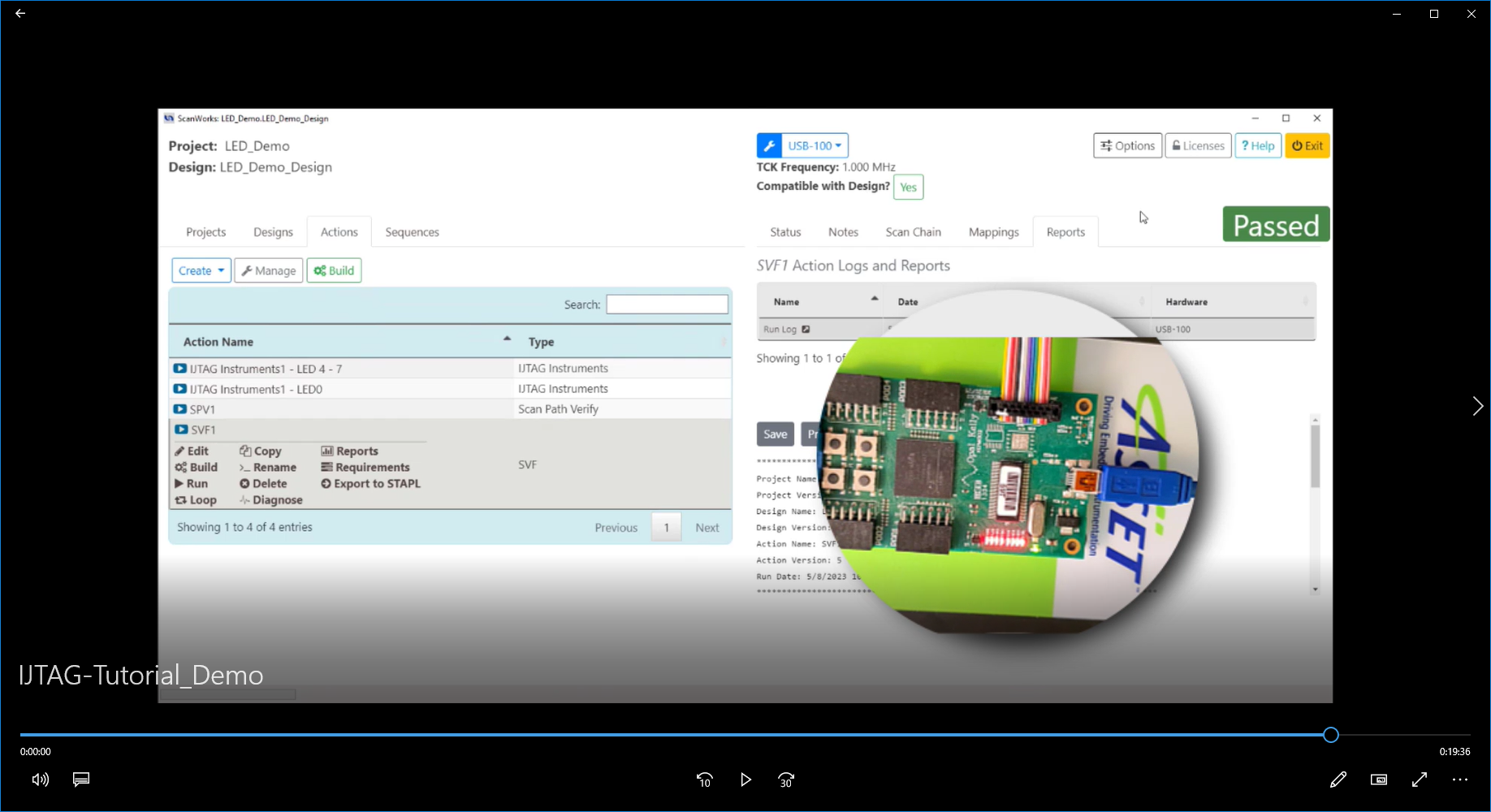

One application to test boards individually or in a system is with ASSET’s Dispatcher Application Programming Interface. The ScanWorks Dispatcher product is a .NET-based API for high-volume board and system-level testing in the manufacturing environment. With Dispatcher, tests can be run and diagnosed remotely to the board and system level.

This webinar focused on setting up and running Dispatcher, demonstrating various use cases, and illustrating how Dispatcher can be used to test multiple boards in a system.

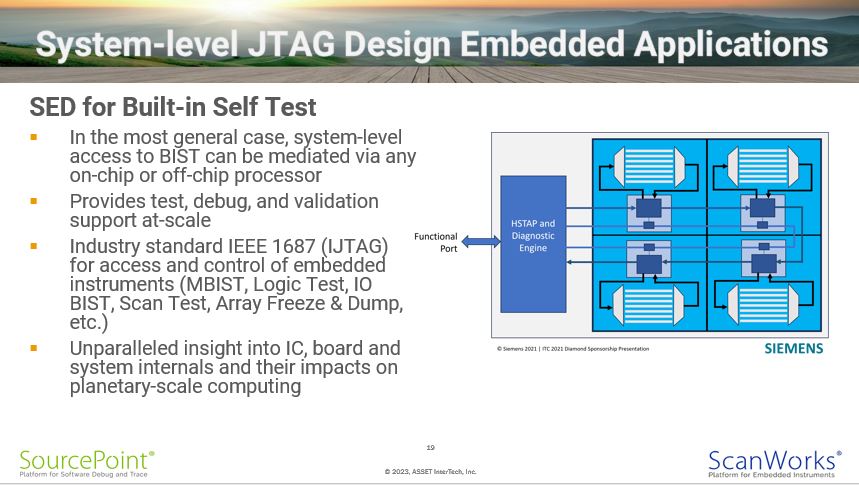

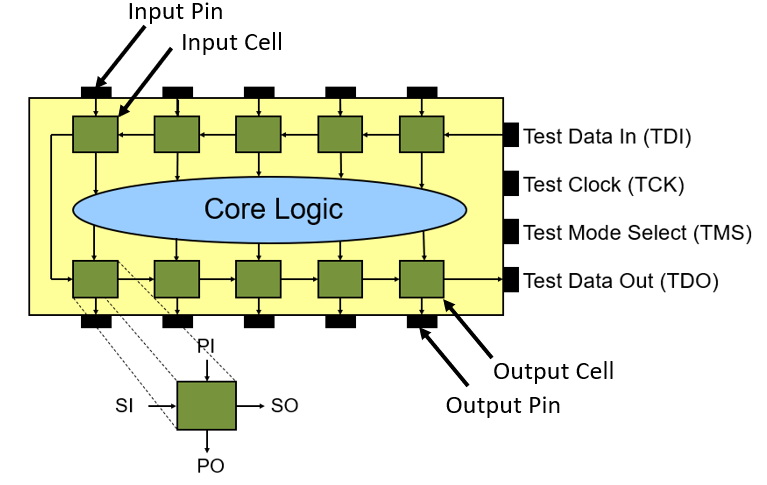

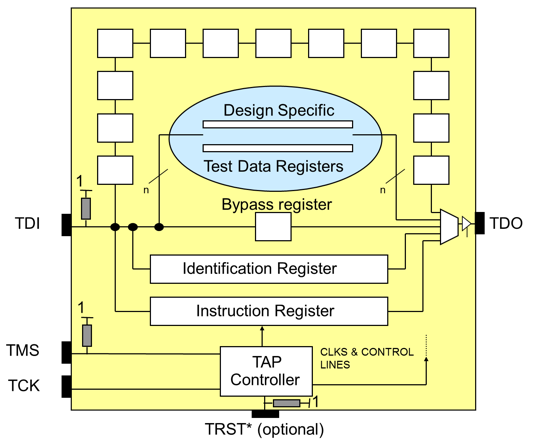

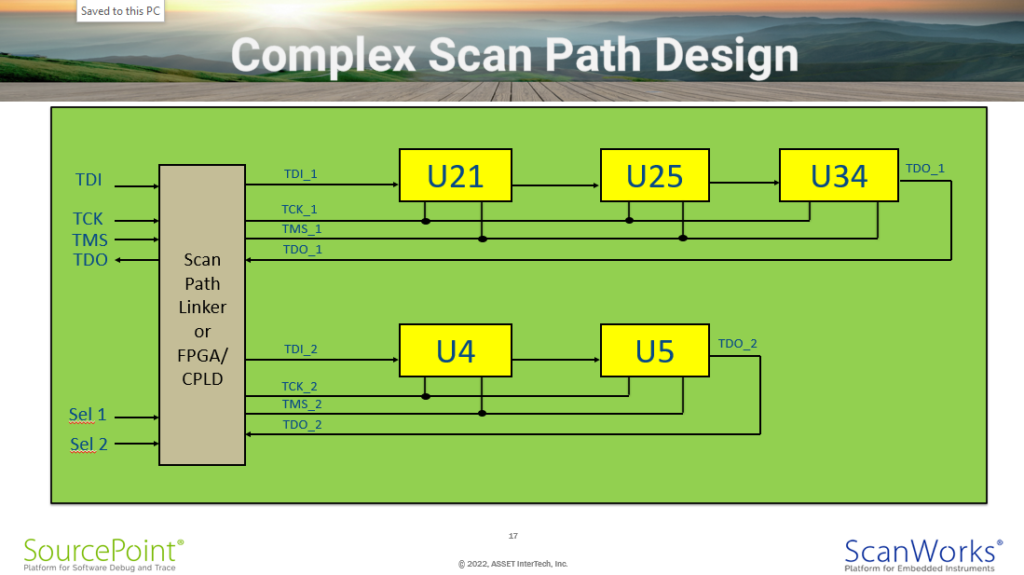

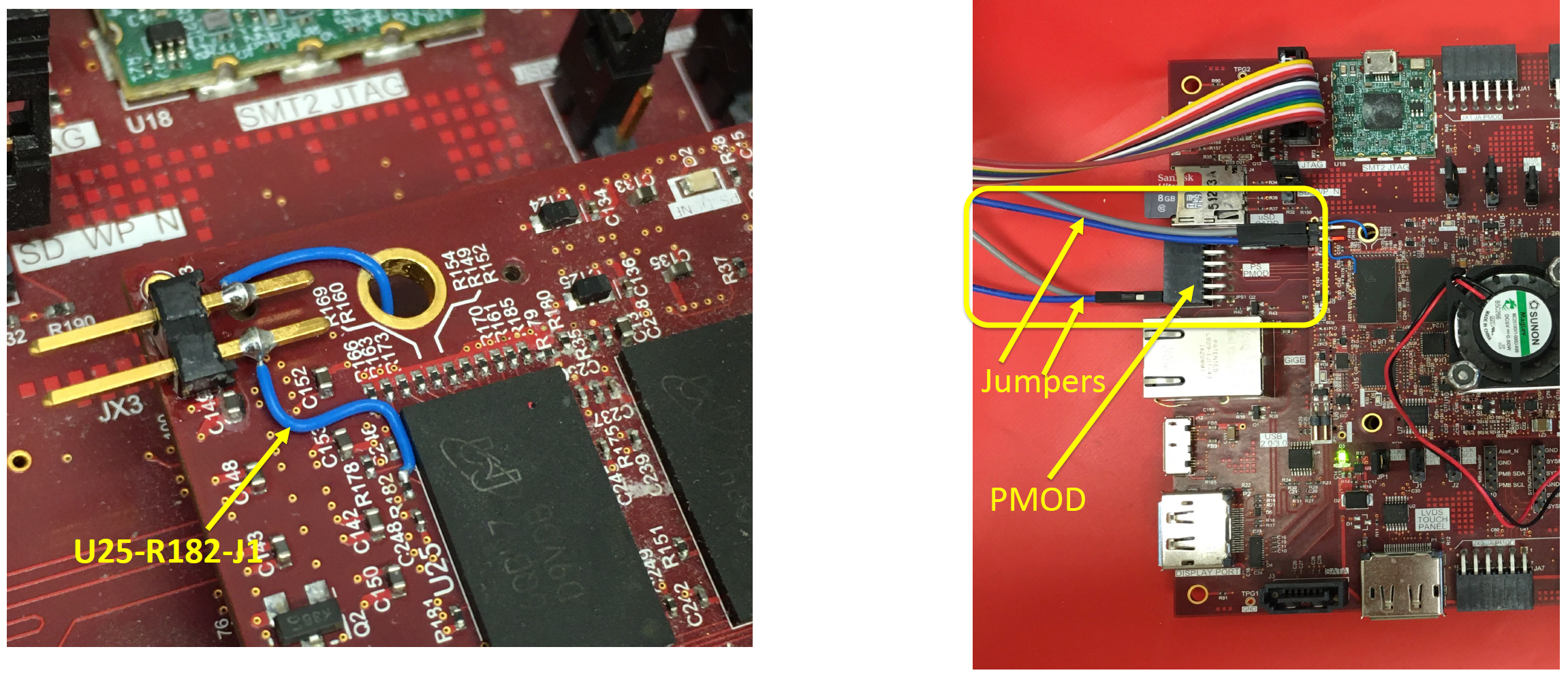

JTAG and boundary scan are technologies that are often thought of in the context of individual chips or printed circuit boards. But, the same technologies can be used in a system-level framework; providing test, debug, programming and validation services in complex structures ranging from multi-chip modules to entire chassis-based board-to-board architectures.

Although thought of most commonly in the context of system-level test, the same technology applies to any application to on-chip Design for Test (DFT), to exercise any kind of Built-In Self Test (BIST)

In this webinar, ASSET’s Michael Johnson described the hardware design rules behind the use of JTAG, boundary scan, and related applications at a system level.

Our colleagues, John Akin and Larry Osborn, have put together this excellent introductory video on the IEEE 1687 (IJTAG) design flow, inserting an IJTAG network and test instruments into an FPGA.

Boundary scan is a software-based means of performing printed circuit board structural testing. Being a non-intrusive test technology based upon embedded instrumentation within chips, it greatly complements other nails-based approaches such as In-Circuit Test and Flying Probe.

Implementing Boundary Scan Design for Test (DFT) guidelines enables the unique capability of accessing onboard test resources for non-intrusive testing, which provides short and open faults coverage.

But, getting the most test coverage out of boundary scan requires board hardware design changes. In this webinar, Part 2 of ASSET’s DFT webinar series, we cover some of the most advanced Boundary Scan DFT guidelines associated with flash memory programming, interconnect testing, and testing with FPGAs.

Webinar presented by Michael Johnson, our JTAG Product Manager.

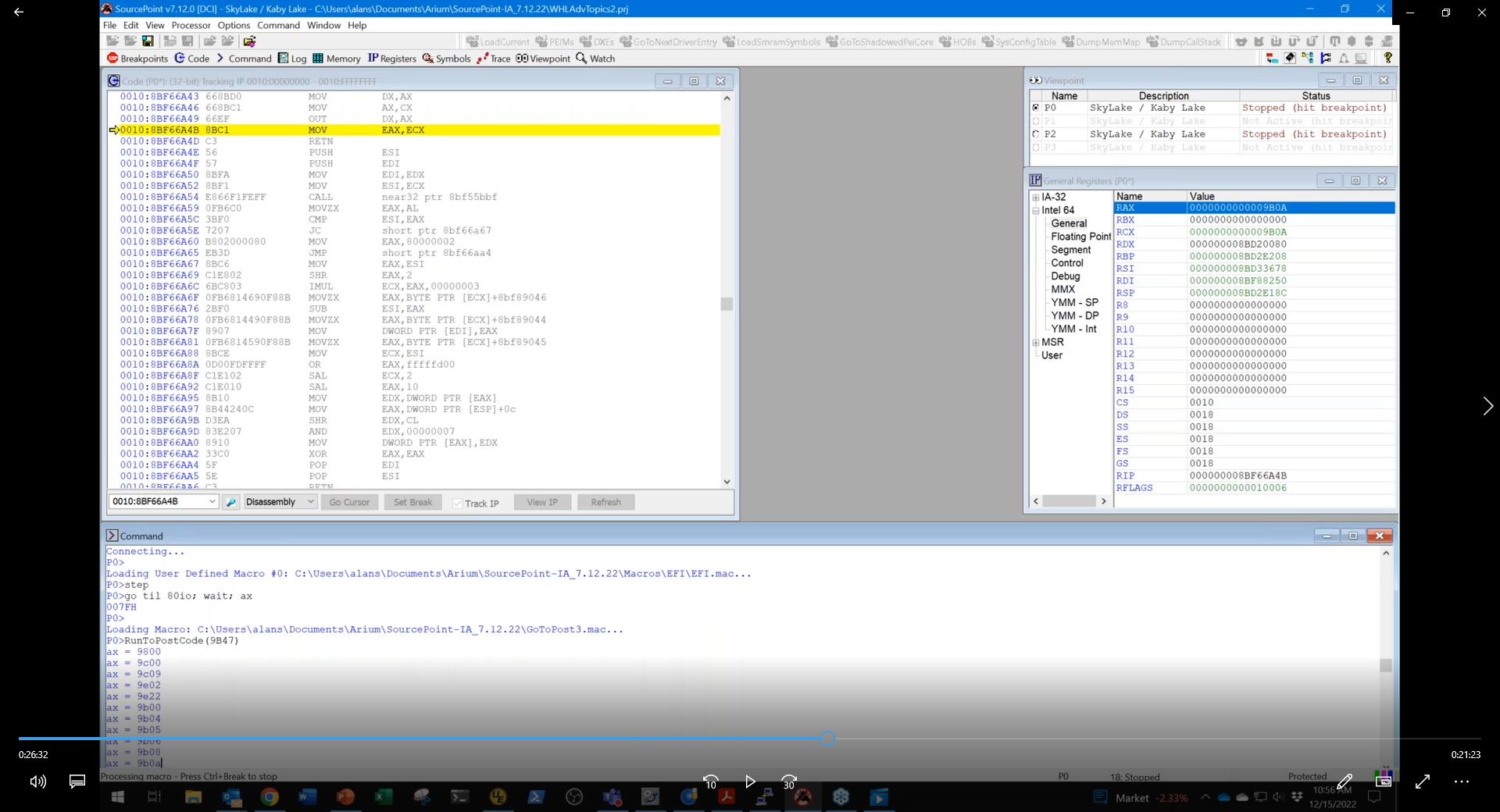

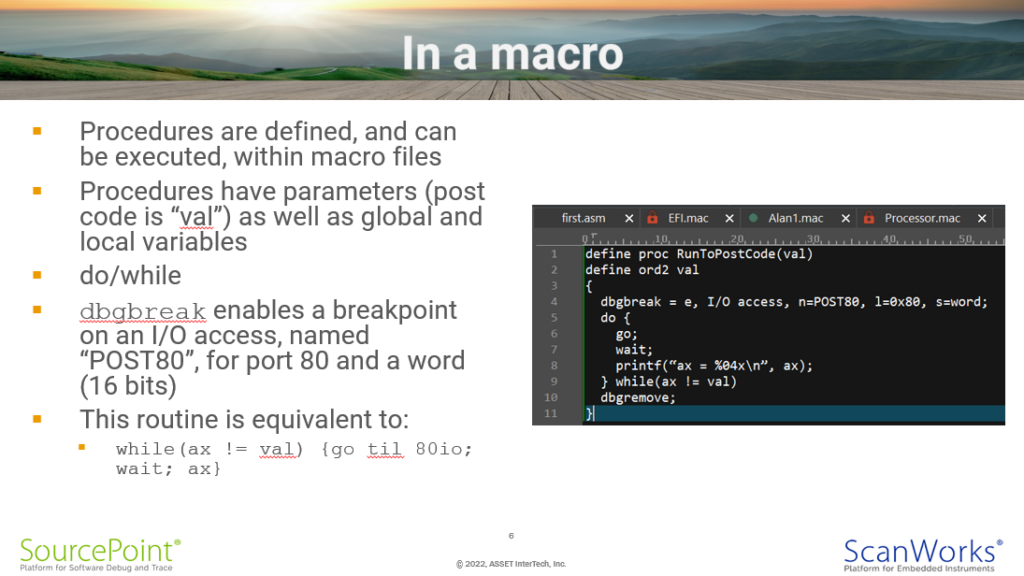

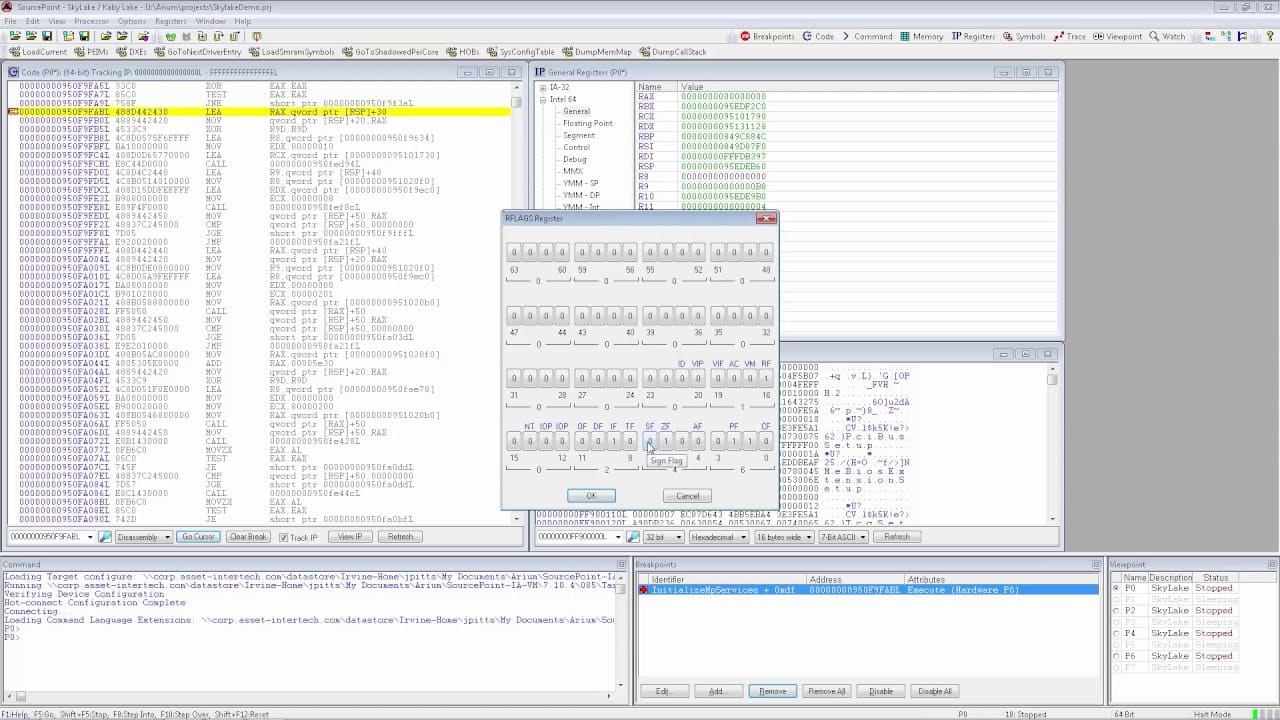

The SourcePoint JTAG-based debugger has support for a very powerful command language. Much of what can be accomplished via the GUI can also be done programmatically, automating many routine debug tasks.

To graduate to SourcePoint “power user” status, it helps to learn the command language, and use it via the command line and via macros.

This webinar presented an introduction to the command language, followed by a demonstration of its use on a live Intel DCI-connected target, and is intended for experienced to expert SourcePoint users.

Boundary scan is a software-based, flexible means of performing printed circuit board structural testing. Being a non-intrusive test technology based upon embedded instrumentation within chips, it greatly complements other nails-based approaches such as In-Circuit Test and Flying Probe.

And being software-based, as opposed to dependent upon “heavy-metal” board testers that use nails, make it extremely cost-effective.

But, getting the most test coverage out of boundary scan requires printed circuit board hardware design changes. This webinar, by Michael Johnson, our JTAG Product Manager, presented the most common to advanced techniques, and there’s something to learn for everyone from JTAG novices to experts.

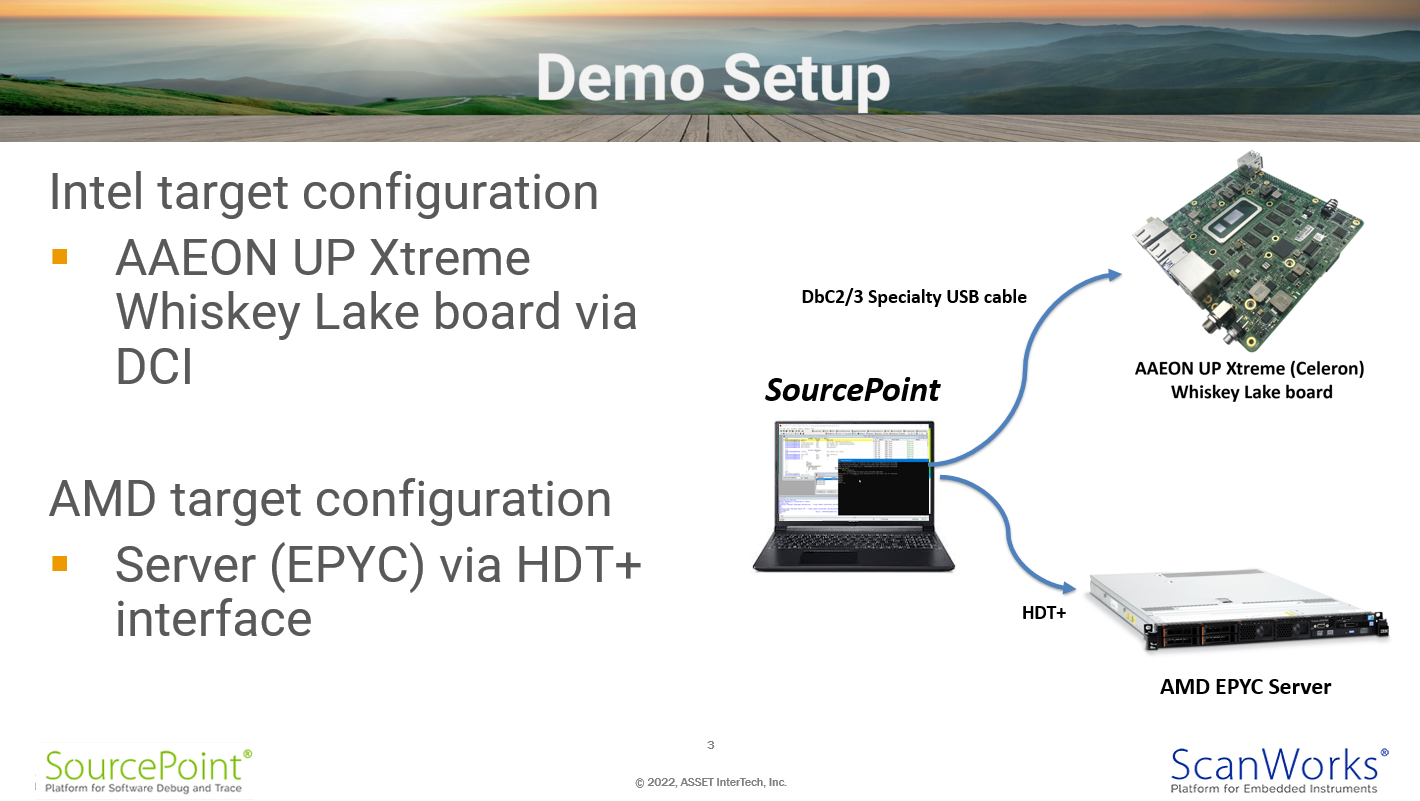

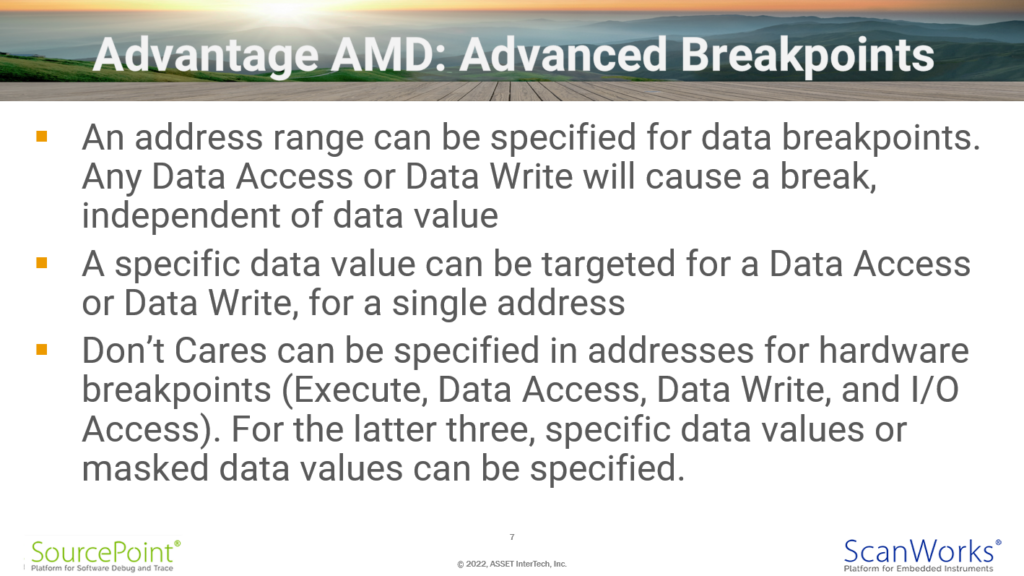

This was one of our most popular webinars yet! ASSET’s Alan Sguigna pitted AMD’s new advanced breakpoint capability against Intel’s powerful trace functionality, inclusive of Processor Trace, Architectural Event Trace and Trace Hub firmware/software trace.

This recording captured the first demonstration ever of a set of conditional hardware breakpoints that AMD has introduced on Genoa: innovating with something new using the normal hardware debug registers for the first time in 30 years!

Midway through, after the live demonstration on both Intel and AMD targets, we asked the audience which IC supplier had the best debugging facilities within their silicon. The answer was surprising!

Testing DDR memories is considered to be one of the biggest design challenges for new product introduction. And faulty memory devices or interconnects account for the majority of design slips and field failures.

This webinar, presented by ASSET’s Larry Osborn, described these bare-metal test and programming technologies in detail. A JTAG-based demonstration on a live target was shown.

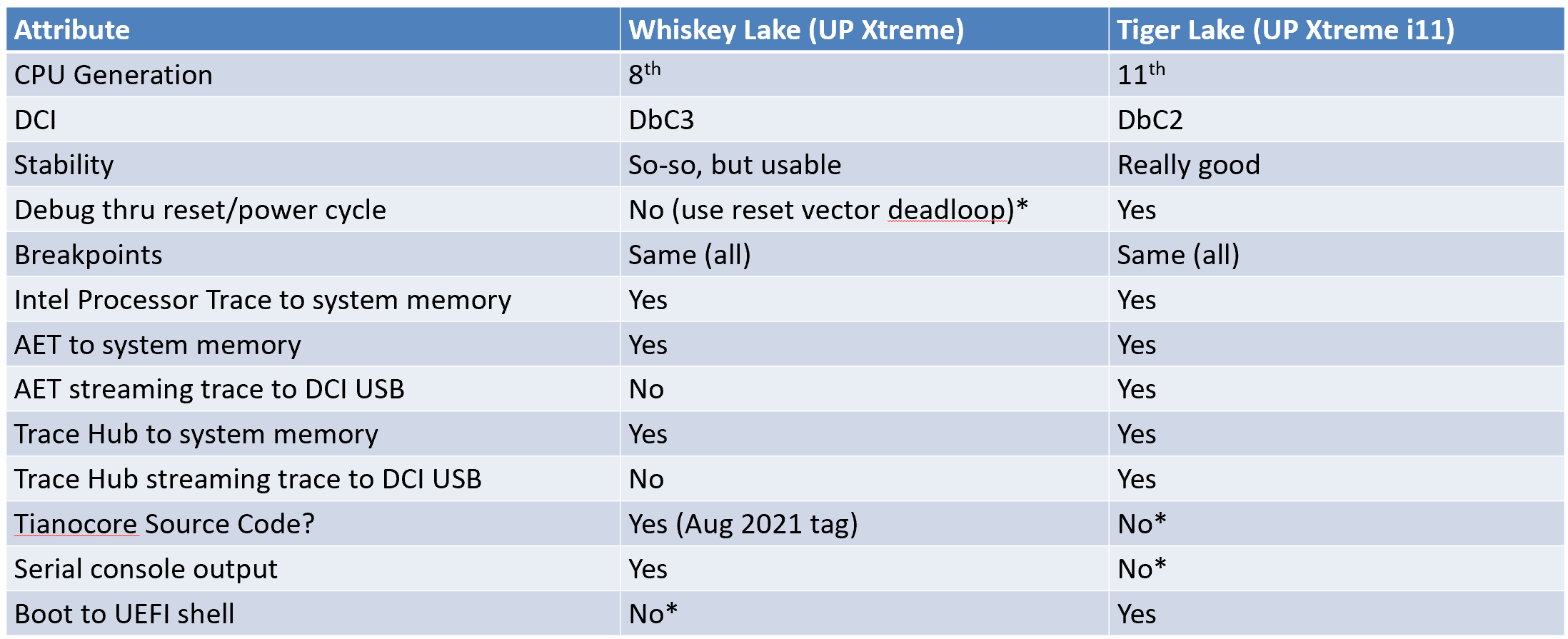

ASSET InterTech’s Alan Sguigna did a live demonstration of UEFI firmware and hypervisor debug on the AAEON UP Xtreme Whiskey Lake and Tiger Lake boards, using our SourcePoint JTAG debugger. Access to the target was via Intel Direct Connect Interface (DCI), eliminating the need for a hardware probe, and connecting solely via a specialty USB cable.

UEFI debug was performed on the WHL MinPlatform open-source build. The hypervisor VM breakpoints were displayed using Satoshi Tanda’s open-source MiniVisor.

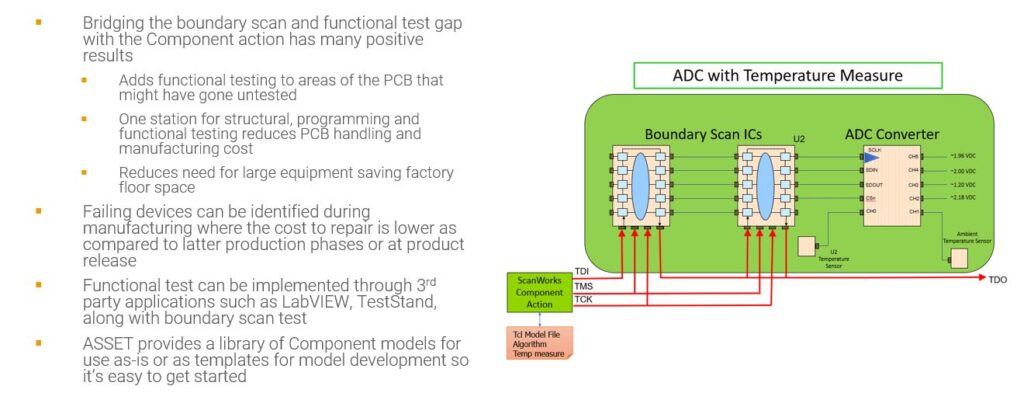

All test engineers want to increase board test coverage. That last ounce can mean the difference between great product quality, and a lot of dissatisfied customers returning your product for repair. Non-boundary scan devices, such as memory devices, ADCs, Ethernet PHY, etc. can be functionally tested with boundary scan using a mechanism named Component Action (CA).

This webinar describes the CA methodology, reviews its programming model, and demonstrates examples on a live target.

Device programming must be fast and efficient to deliver the performance necessary to achieve Design and Production Line goals. Offboard programming approaches are burdened by device inventory and change order issues. And historically, JTAG/boundary-scan has been a great solution for onboard programming of small images, but is too slow for today’s large flash devices.

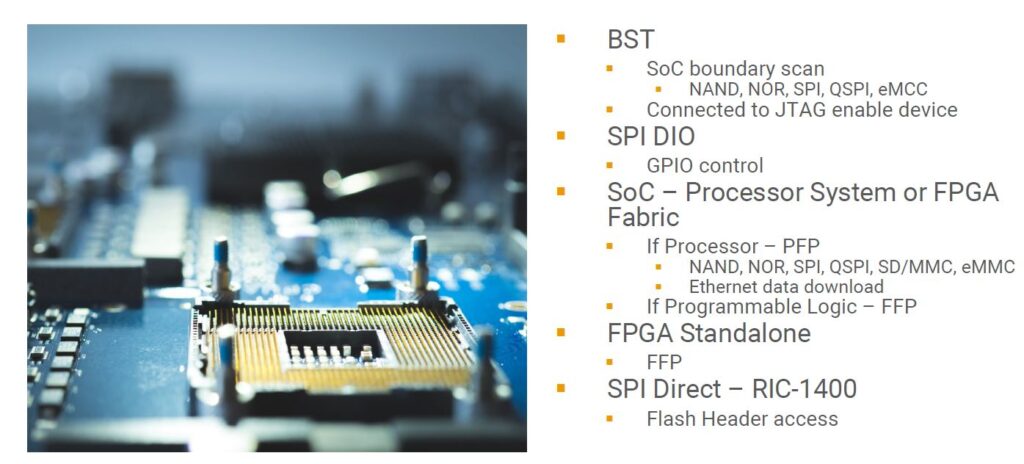

This webinar describes new innovations in onboard programming that dramatically reduce programming times, and thus lower the cost of the development and manufacturing programming processes. Technologies such as short-chain boundary scan, FPGA-based fast programming, SPI Direct, and processor-based fast programming (using JTAG and/or Ethernet) are reviewed and demonstrated.

Latent structural faults may be undetectable by traditional functional test, manifesting themselves via system failures in the field, which is unacceptable for mission-critical applications. This dictates a new approach to built-in test: using JTAG-based boundary-scan test (BST) within system firmware, thereby eliminating the need for external physical hardware probes, and providing an in-situ mechanism for failure prevention and proactive maintenance.

This webinar describes the application of JTAG for Built-In Self Test, the technology behind it, Test Access Port (TAP) controller firmware requirements, the BST library Application Program Interface (API), and hardware design requirements.

Webinar recording: At-Scale BMC-based debug of x86 servers

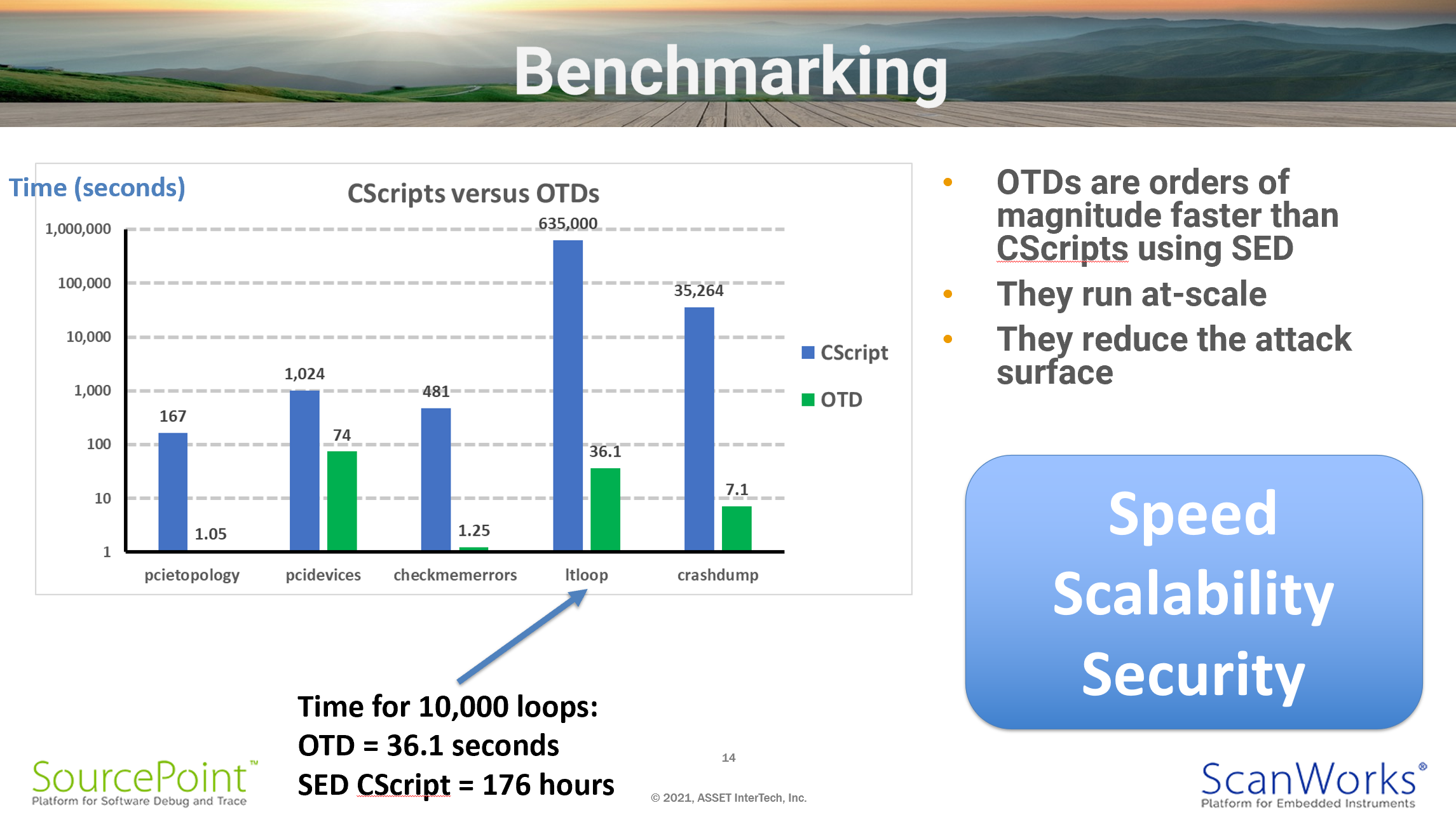

Want to see some Intel Python CScripts ported to 'C' and running on a BMC on a live Intel server? This webinar, presented by ASSET's Alan Sguigna, includes a demonstration of embedded JTAG remote debug on a live Intel server platform. You'll see applications like low-level memory error checks, PCIe stress testing, and JTAG-based autonomous crash dump in action.

Webinar recording: JTAG-based debugging of AMD EPYC servers

Datacenter-scale deployment of AMD EPYC processors demands better debugging tools. Low-level firmware issues can manifest themselves in the most intermittent, difficult-to-duplicate bugs. This recorded webinar video demonstrates the advanced use of source-level and symbolic debug tools to identify silicon, hardware, firmware and software issues.

Webinar recording: Chiplet interconnect testing using JTAG/boundary scan

This is the December 2nd, 2020 webinar recording of the use of ScanWorks STIL export functionality to perform chiplet interconnect testing. The use of IEEE 1149.1 and 1149.6 for high-speed interconnect structural testing allows for detection and diagnosis of process issues on chiplet-based designs.

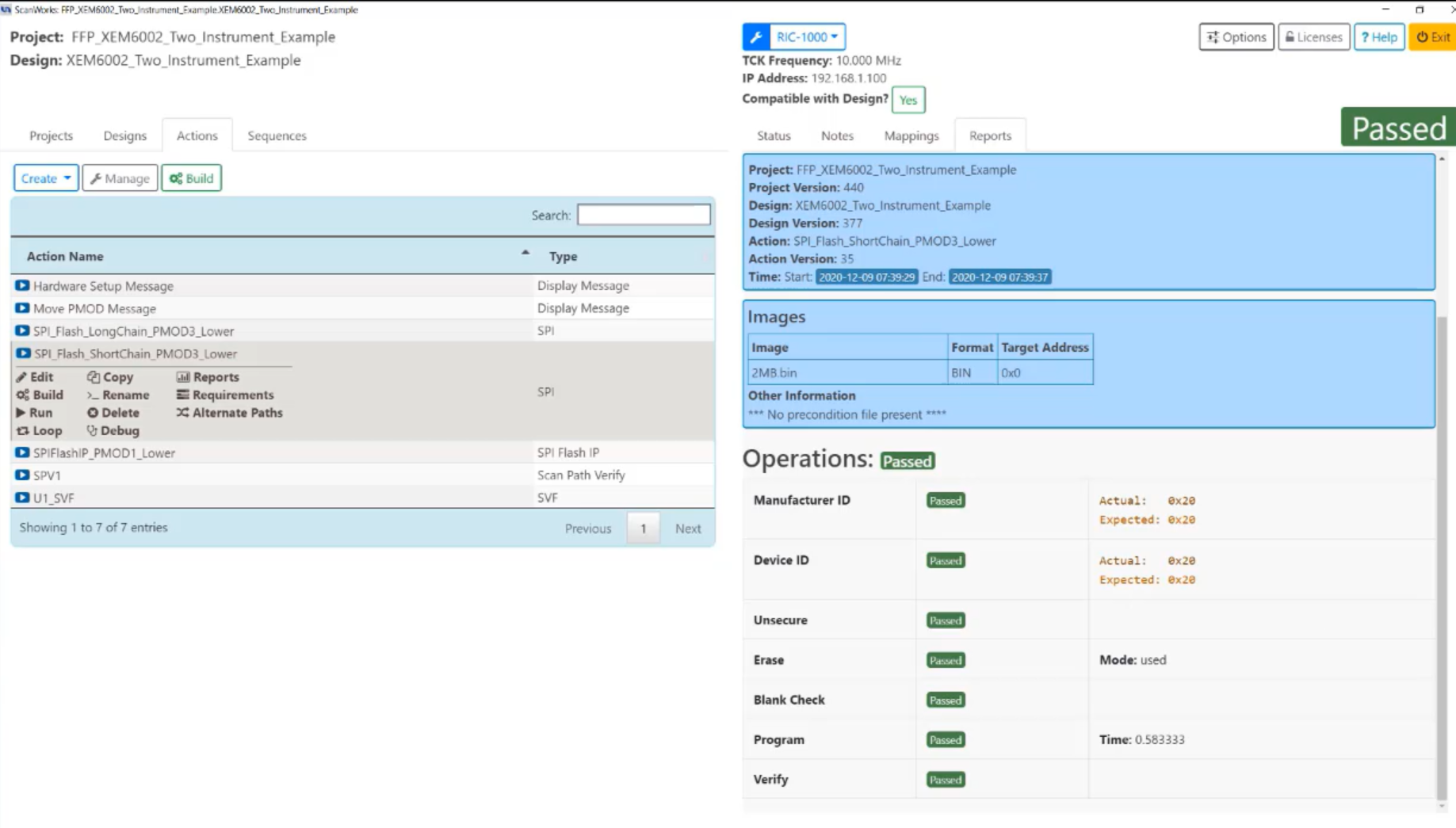

Fast Flash Programming using FPGA IP

JTAG/Boundary Scan is a useful technology for programming flash memories, but it can be slow. This video demonstrates the use of FPGA-based IP to dramatically reduce the time to do device programming...

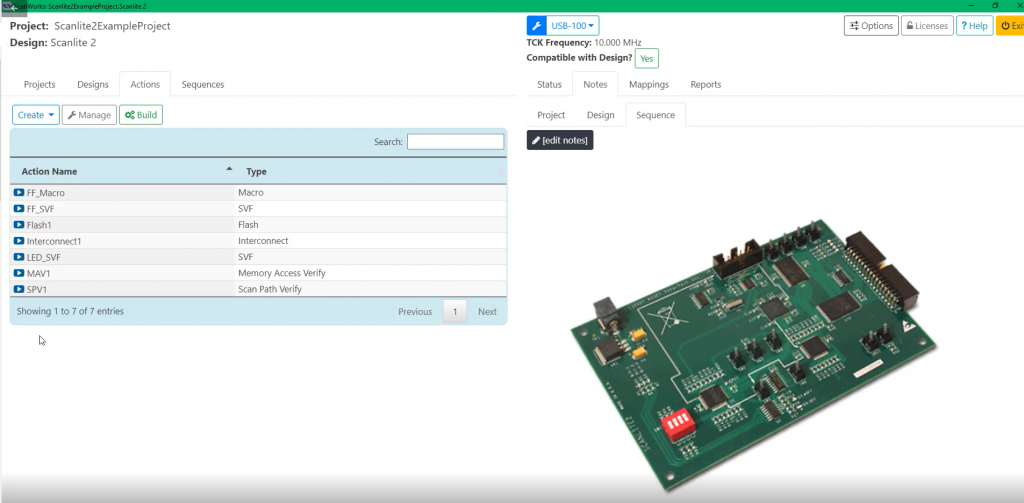

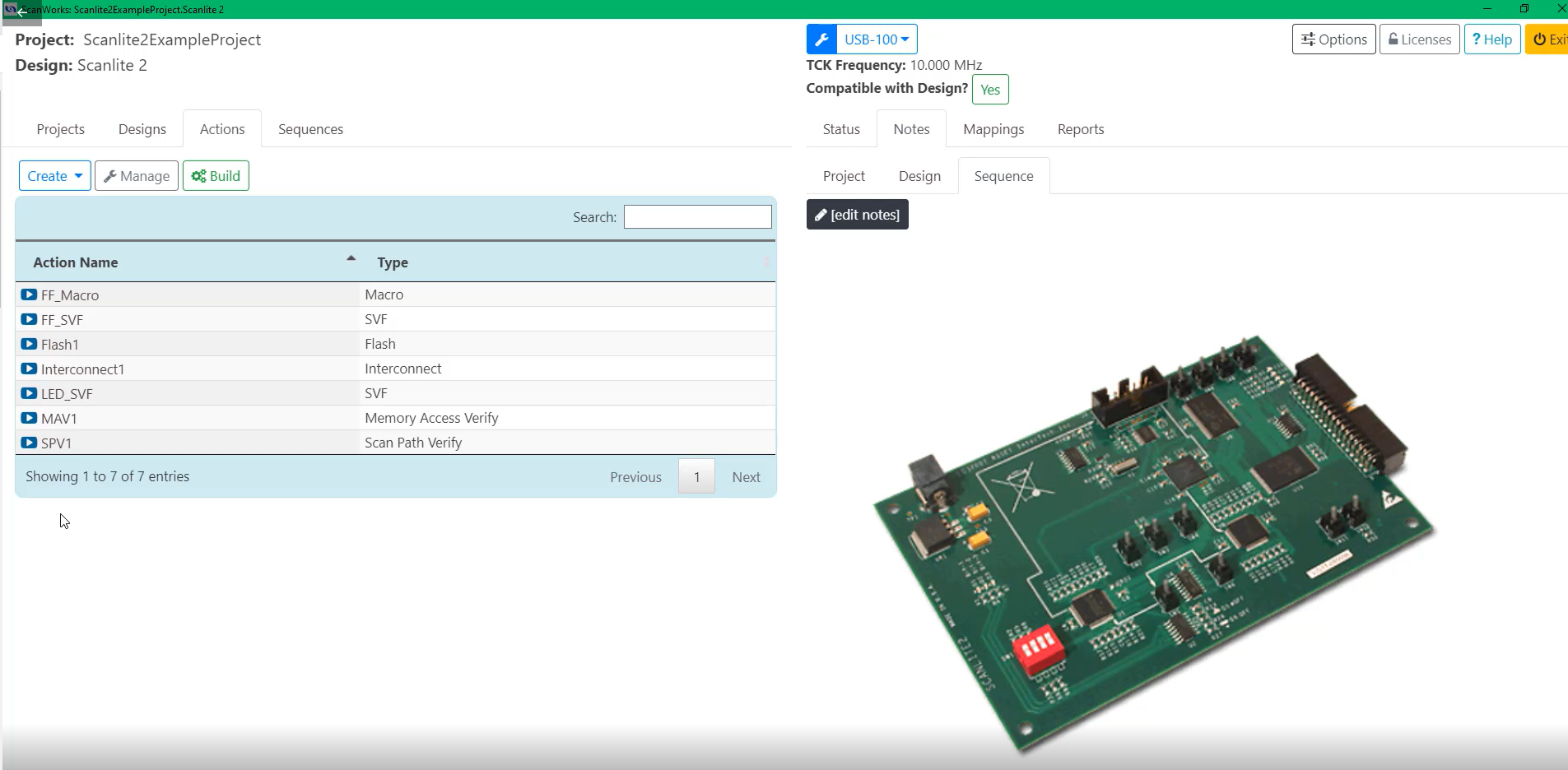

ScanWorks for Boundary-Scan Test Graphical User Interface Overview

This video demonstrates the value of Boundary-Scan Test software. Test engineers can quickly develop interconnect tests and device-programming actions for use on first prototype board to accelerate the board bring-up process. Then tests can be exported for use in manufacturing and repair facilities.

SourcePoint licensing and installation

This short video walks you through the SourcePoint installation and licensing process.

Processor-based Fast Programming for TI Power Management UCD3138 demo

ScanWorks® Processor-based Fast Programming uses a target agent that is task specific to configure embedded controllers to gain access to the flash components. By using On-Chip Memory (OCM)…

Processor-based Functional Test for DDR Zedboard tune and test

This video will cover DDR calibration or tuning on the Zedboard and follow-up with the DDR testing after applying the tuning results.

SABRE Lite DDR3 Tuning using Processor-based Functional Test for DDR

ScanWorks® Processor-based Functional Test for DDR addresses design and production challenges of tuning, calibration and optimization of DDR settings.

Zedboard episode 3 vlog, part 1

This episode is all about the Zedboard QSPI. Starting with a hardware review of the board, the QPSI device…

Zedboard episode 2 vlog

This episode will cover the DDR initialization via macros, reverse-engineer said macros, explore where in the Xilinx tools to extract the data necessary for debugging, and explore where to find…

Zedboard episode 1 vlog - with the ASSET SourcePoint debugger

Video Chronicles to explore the Zynq-7000 All Programmable SoC from Xilinx. Episode One covers booting the Zedboard and connecting SourcePoint debugger to the DAP interface and conducting dual core control.

SourcePoint for Intel product demo

This video shows the full SourcePoint GUI, with its source-level debug capabilities.

IJTAG Value to Silicon Designers and Board Designers

This video shows the value of IJTAG (IEEE 1687) to the Silicon Designer and the Board Designers. There is no audio on this video.

Embedded Instrumentation Trends Drive Non-intrusive Board Test

By Electronics Technology Forum*: With growing circuit density, comes greater complexity and…

ASSET | Arium - ARM tools: new synergies, more value, part 3

Software debug tools for ARM processors in SoCs including enhancements to ARM’s System Trace Macrocell (STM) and others will be the outcome of the recent merging of ASSET InterTech and Arium. The…

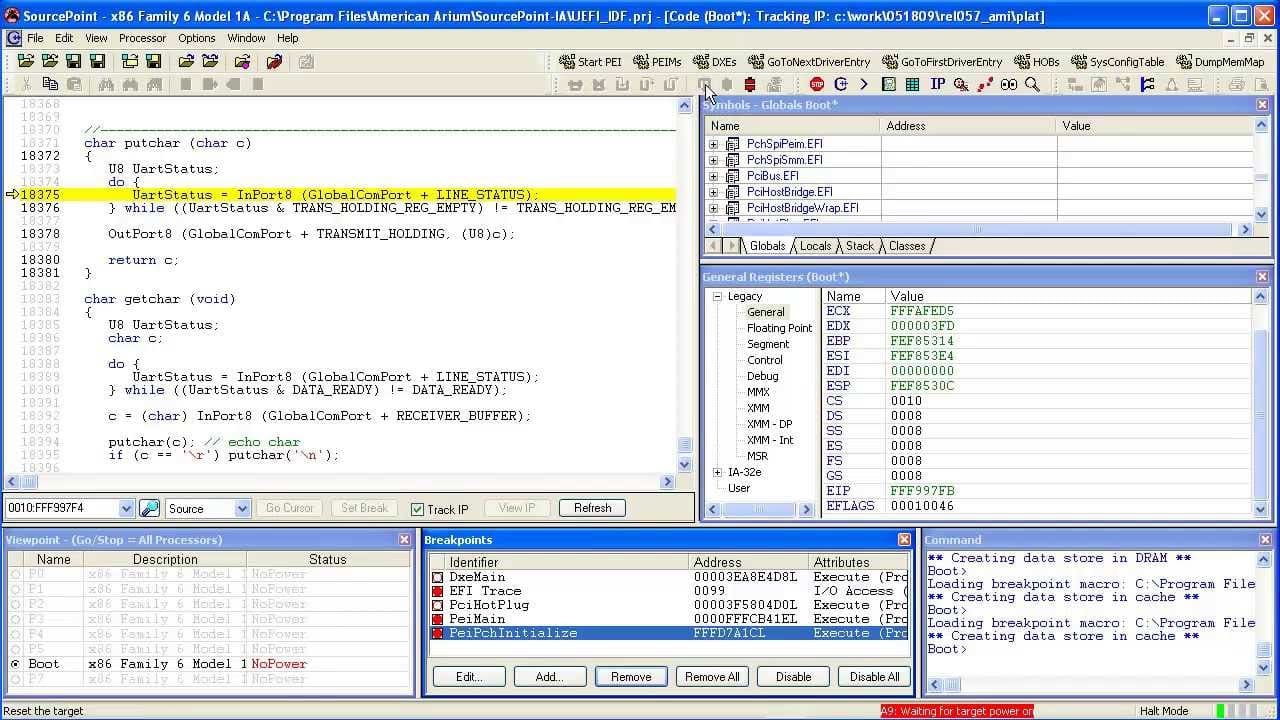

More Visibility into Arium SourcePoint UEFI debugging

Using SourcePoint® to empower the developer to debug UEFI code quickly and find the root cause to execution problems. BIOS development was an art and now more of a science but a complex…

ASSET | Arium - Embedded instrumentation trends, part 2

From software debug to hardware test and validation, the scope of embedded instrumentation has continued to expand. Glenn Woppman, president and CEO of ASSET InterTech, discusses how an inside-out

ASSET and Arium Merge - track and trace

Track & Trace of soft and hard problems in boards and SoC’s. Stronger support for Intel and ARM based designs. The ScanWorks platform breaks new ground with the SourcePoint software debug…

ScanWorks® Non-intrusive Board Test (NBT)

ScanWorks® Non-intrusive Board Test (NBT) from ASSET InterTech is a comprehensive solution for testing, debugging and validating the latest circuit boards that use highly-integrated,…

ScanWorks® Embedded Diagnostics

ASSET’s ScanWorks® Embedded Diagnostics solution improves the reliability of high-availability and mission-critical systems. It allows the root causes of hardware and software failures to be…