## Real Insight from Code to Silicon

SourcePoint<sup>®</sup> ScanWorks<sup>®</sup> Squeezing Out More Test Coverage: **Bridging the Gap Between Boundary Scan and Functional Test** Michael R. Johnson ScanWorks BST Product Manager/Support Manager August 31

## Agenda

- Test Coverage Considerations

- Coverage Assessment Methodology

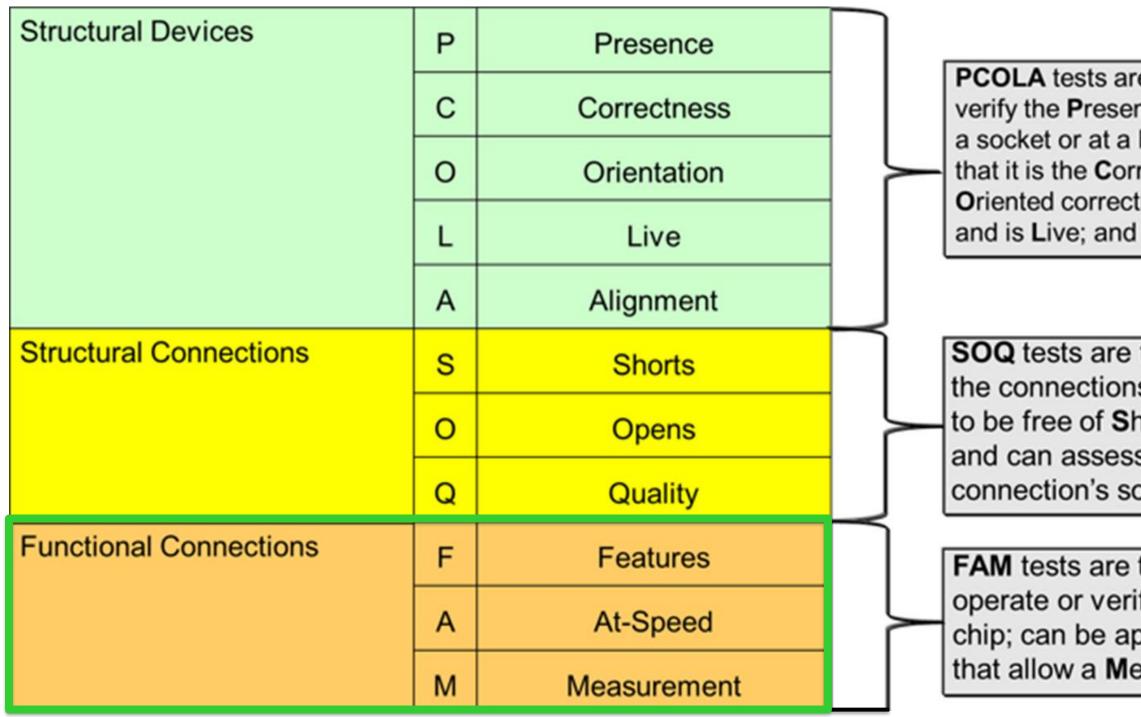

- iNEMI PCOLA/SOQ/FAM Framework

- Bridging the Gap with the Component Action

- Functional Test with the Component Action

- Component Action Facts

- Component Model Structure

- Component Model Base Commands

- Functional Test Examples

- Demonstration

- Summary

### **Test Coverage Considerations**

- Every PCB manufacturer would like to have 100% test coverage of their PCBs, but is this achievable?

- In manufacturing and test environments, time is money; PCB manufacturers must decide how much of each they are willing to invest to ensure a quality product

- PCB manufacturers must decide what percentage of PCB rejects and returns are acceptable due to reduced or untested areas of the PCB

- Each PCB manufacturer must decide what determines maximum test coverage for their product

# **Coverage Assessment Methodology**

- When asked, engineers will say the goal of a PCB test plan is 100% coverage

- Achieving maximum test coverage is an iterative process with coverage being improved with each "turn" or redesign of the PCB

- Following design for test (DFT) guidelines during PCB design and layout produces maximum coverage

ScanWorks®

# **Coverage Assessment Methodology**

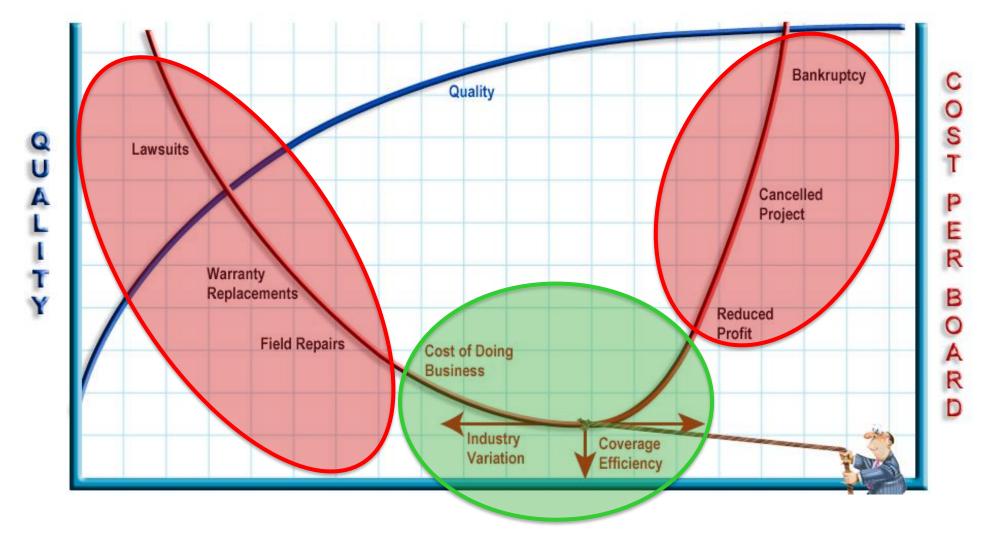

- Coverage that is too low will result in warranty returns and high cost of product replacements in the field

- Coverage that is too high becomes expensive and can affect a product's total cost, driving up price and making it uncompetitive in the market

- The goal becomes achieving optimum test coverage (i.e., best coverage achievable given those restraining factors)

### **Coverage Optimization**

ScanWorks® Platform for Embedded Instruments

| board location;<br>rect chip; and is<br>tly; receives power | Boundary Scan<br>Tests and External<br>Equipment (ICT,<br>X-Ray) and Visual<br>Inspection |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| IOUS AND ODENS | Boundary Scan<br>Interconnect Test<br>and X-Ray |

|----------------|-------------------------------------------------|

|----------------|-------------------------------------------------|

|--|

### Bridging the Gap with the Component Action

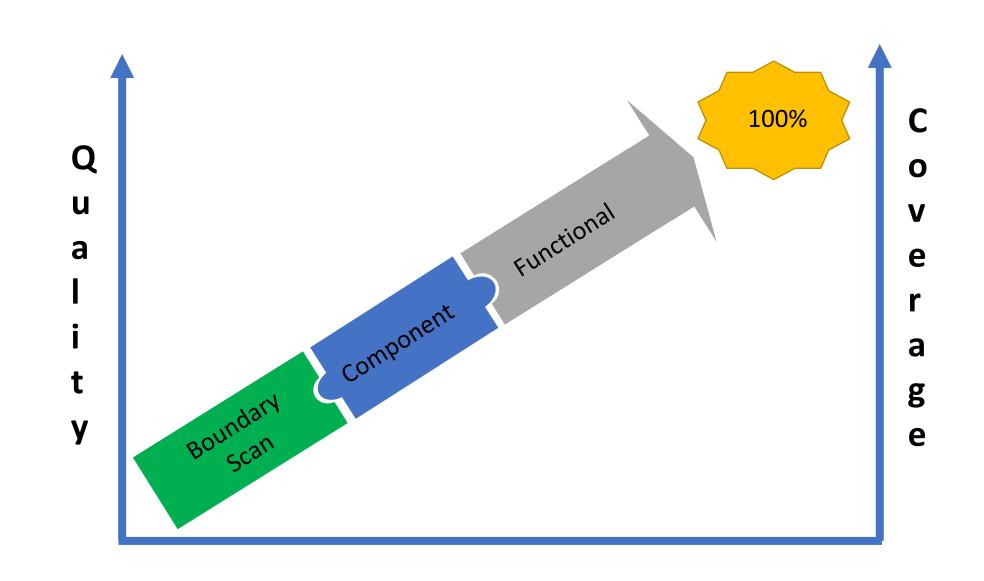

- PCB functional test coverage can be realized by using boundary scan

- The ScanWorks

Component Action can

"bridge the gap" between

boundary scan and

functional test to enhance

PCB test coverage

### **Functional Test with the Component Action**

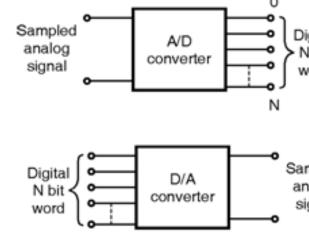

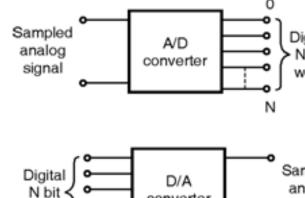

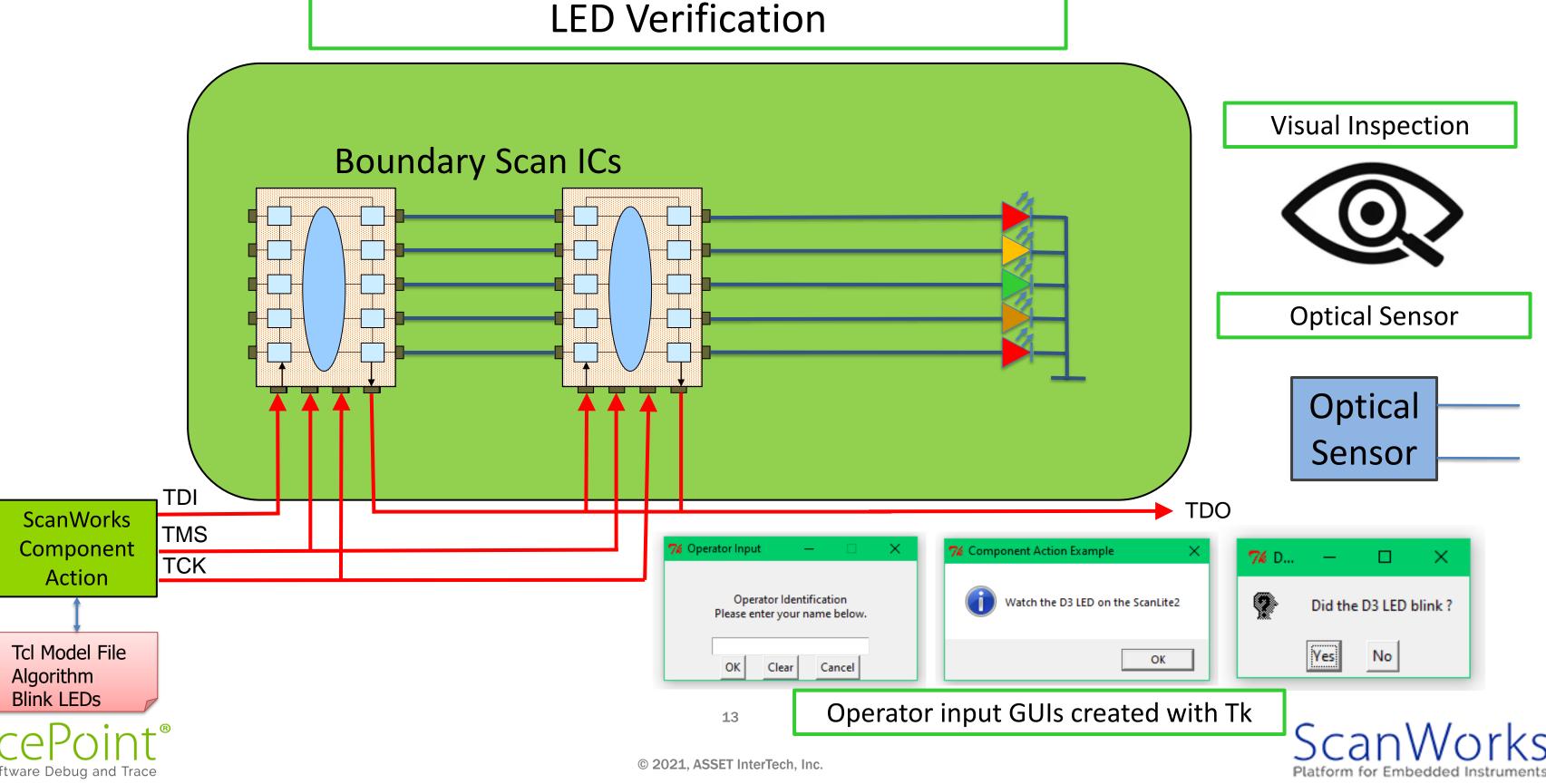

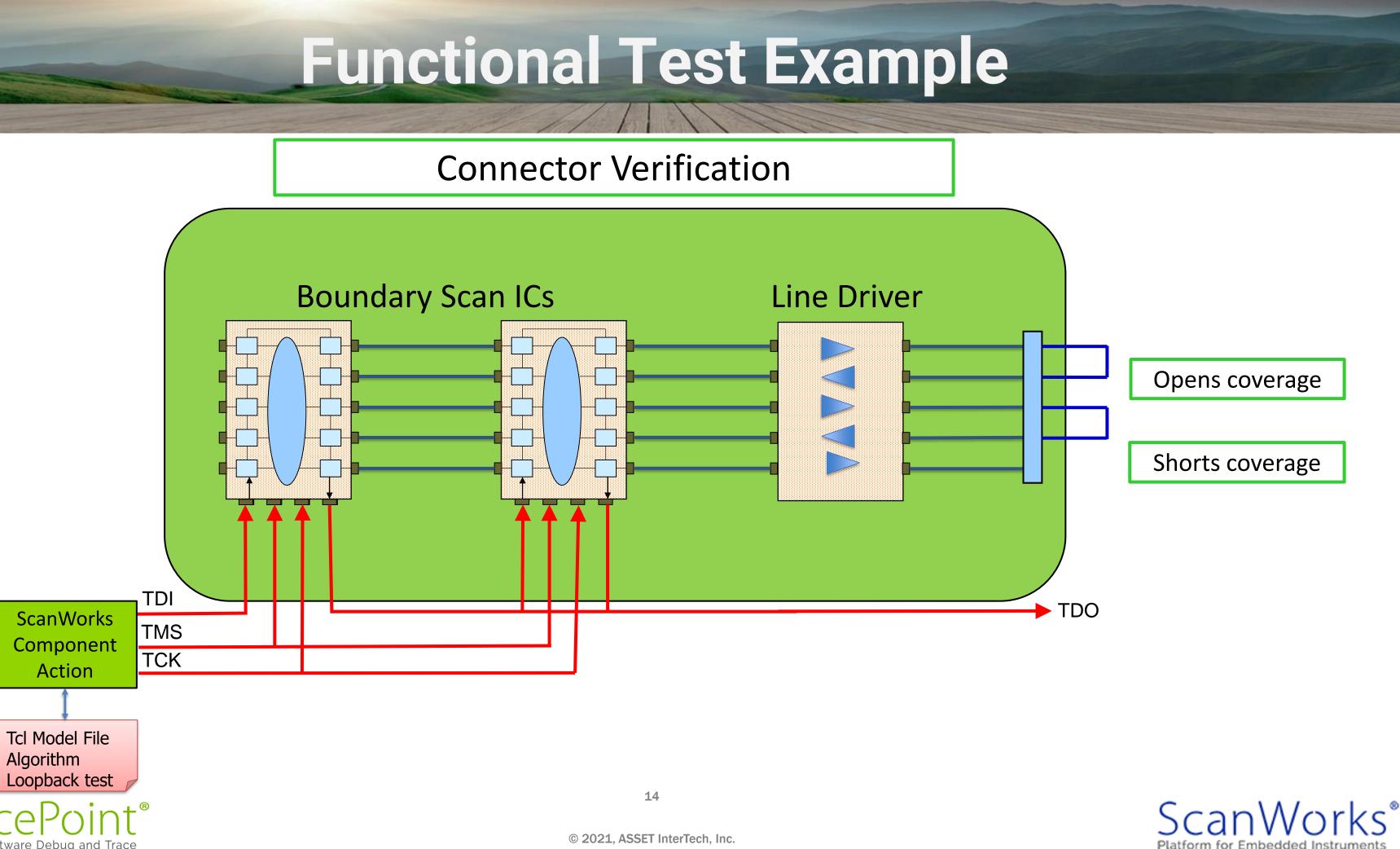

- The ScanWorks Component action is a general-purpose action that extends functional test coverage to a wide array of non-boundary scan devices

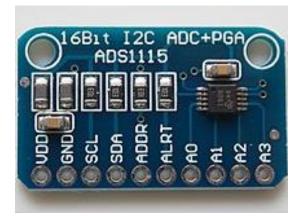

- ADCs/DACs

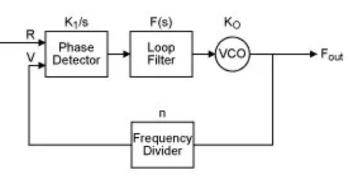

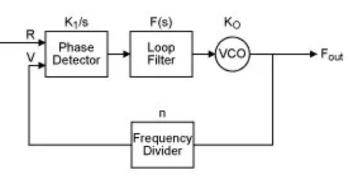

- Oscillators, clocks, PLLs

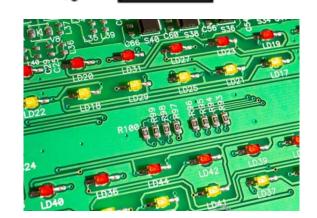

- LEDs

- Connectors

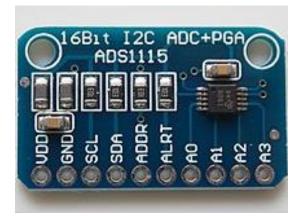

- l2Cs

- Ethernet PHYs

- Switches

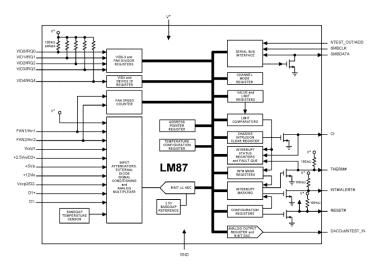

- System monitors

Digital N bit word

Sampled analog signal

toggle switch

push button switch

ScanWorks®

### **Functional Test with the Component Action**

word

- The Component action uses the Tool Command Language (Tcl or Tickle) programming language along with a PCBs existing boundary scan resources to access non-boundary scan devices

- Any non-boundary scan device with boundary scan access, and an algorithm that can be modeled from its data sheet through Tcl, is a candidate for functional testing by the **Component** action

converter

Digital N bit word

Sampled analog signal

push button switc

## **Component Action Facts**

- The Tcl interpreter is included in ScanWorks

- The Tk package is also included in ScanWorks for creation of dialogs and GUIs

- Component models define the pins on the target device that require boundary scan access

- Component models are based on the operational algorithms of the non-boundary scan devices

- Component models are available for download from the ScanWorks Model Library for use as-is or as templates for model development

Models

Atmel\_at93c46b\_64x16\_ver5.tcl

AT93C46B 3-Wire Serial E2PROMs 1K (64 x 16)8

atmel\_at93c66a\_256x16\_ver4.tcl

AT93C46B 3-Wire Serial E2PROMs 1K (64 x 16)8

Broadcom\_BCM5482\_PHY\_BGA.tcl

External loopback test for BCM5482, both PHYs.

Broadcom\_BCM5785\_XOR.tcl

XOR-tree test on one of the three XOR-trees or

CY6264.tcl

This Component Model does a data bus test of

set f [open \$vectorFileName "w"] puts \$f "VECTOR ADDRESS 10 9 8 7 6 5 4 3 2 25 24 23 21" puts \$f "VECTOR DATA 19 18 17 16 15 13 12 11" puts \$f "VECTOR WE 27" puts \$f "VECTOR CE 20" puts \$f "VECTOR OE 22" close \$f

# read the data bus

set actualBusValue [ca readBus DATA]

puts "DATA bus value is \$actualBusValue"

if { \$actualBusValue != \$expectedBusValue(\$i) } {

puts "Test failed: expected a data bus value of \$expectedBusValue(\$i)"

set returnValue 1

|                                                              | Date Posted                 |

|--------------------------------------------------------------|-----------------------------|

| )8-Pin PDIP and JEDEC SOIC Packages                          | September, 26 2012 08:58:00 |

| )8-Pin PDIP and JEDEC SOIC Packages                          | September, 26 2012 09:07:00 |

| <b>cl</b><br>/s.                                             | May, 03 2013 02:48:00       |

| on the BCM5785 southbridge.                                  | May, 03 2013 02:49:00       |

| of the Cypress CY7C128A static RAM device on ScanLite board. | April, 05 2012 09:19:00     |

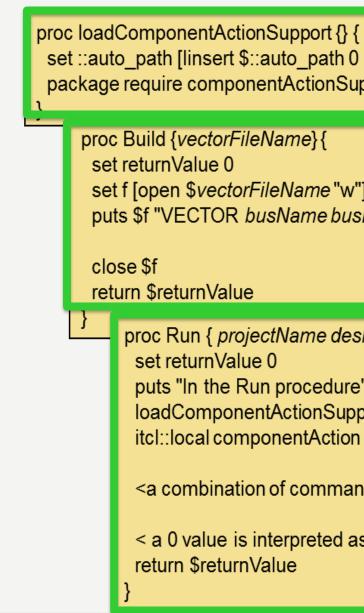

### **Component Model Structure**

- The Proc loadComponentActionSupport procedure loads all of the necessary ASSET Component Action classes when the action is run

- Pins on the target non-boundary scan device to be functionally tested are listed in the proc Build procedure

- This information is used along with UUT netlist to find access to the target nonboundary scan device

- The proc Run procedure defines the algorithm necessary to functionally test the target non-boundary scan device

- Uses the buses defined in the proc Build and the user-supplied commands to communicate with the target non-boundary scan device

Modelname.tcl

set ::auto\_path [linsert \$::auto\_path 0 \$::env(ASSET)\\ComponentActionSupport] package require componentActionSupport

set f [open \$vectorFileName"w"] puts \$f "VECTOR busName busPins"

proc Run { projectName designName actionName } {

- puts "In the Run procedure"

- IoadComponentActionSupport

- itcl::local componentAction ca \$projectName\$designName\$actionName

<a combination of commands to test the target device>

< a 0 value is interpreted as a Pass and a non-zero value is interpreted as a Fail>

# **Component Model Base Commands**

- Command: setBus

- Sets the TDI buffer for the boundary scan cells used to access the pins of the non-Boundary Scan device

- Command: disableBus

- If possible, disables the boundary scan driver cells used to drive the pins

- Command: DRScan

- Performs a DR scan to scan in the contents of the TDI buffer and captures the data in the TDO buffer that is scanned out

- Command: readBus

- Performs a DR scan and reads the data from the TDO buffer for the bus pin

- See the documentation "Using Component Actions" at c:\scanworks\doc for more information

### **Functional Test Example**

### **LED** Verification

Platform for Software Debug and Trace

Platform for Software Debug and Trace

### **Functional Test Example**

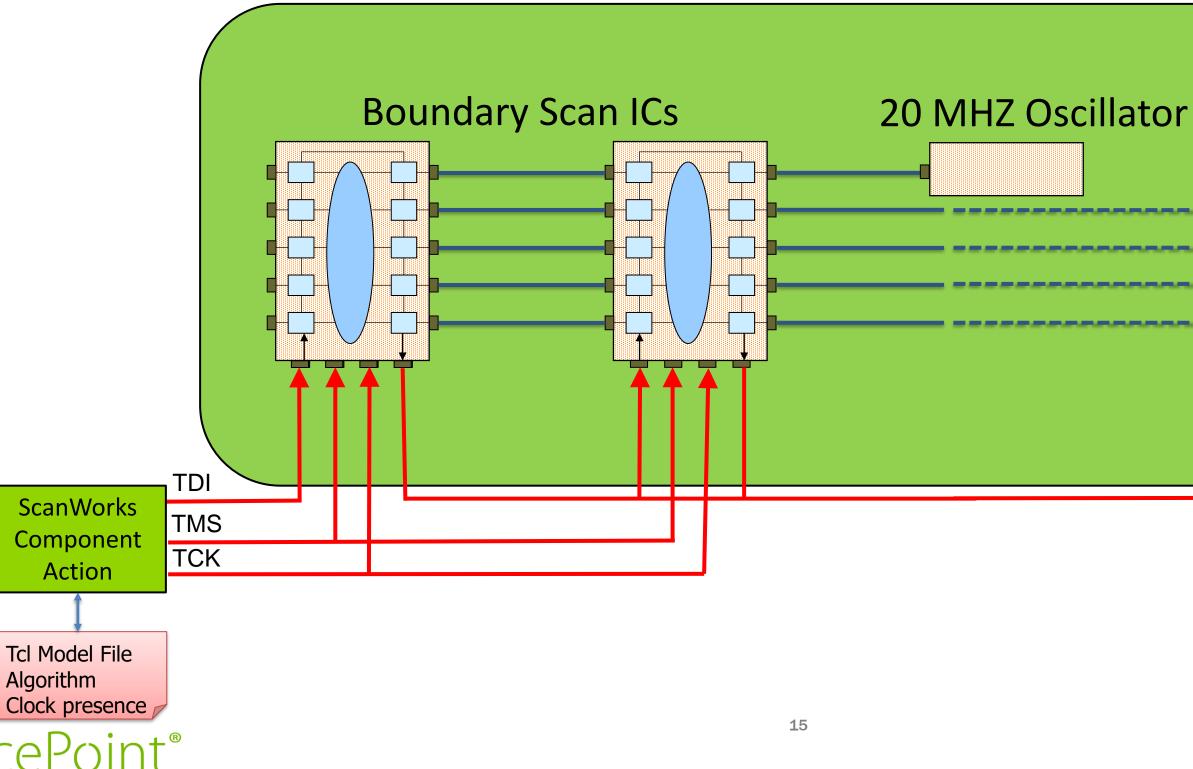

### **Clock Verification**

Platform for Software Debug and Trace

© 2021, ASSET InterTech, Inc.

Test for oscillator clock transitions

**TDO**

### **Functional Test Example**

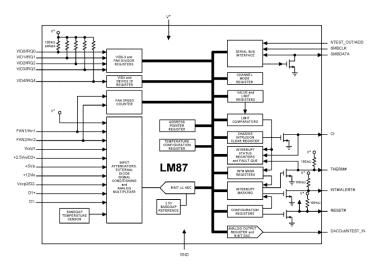

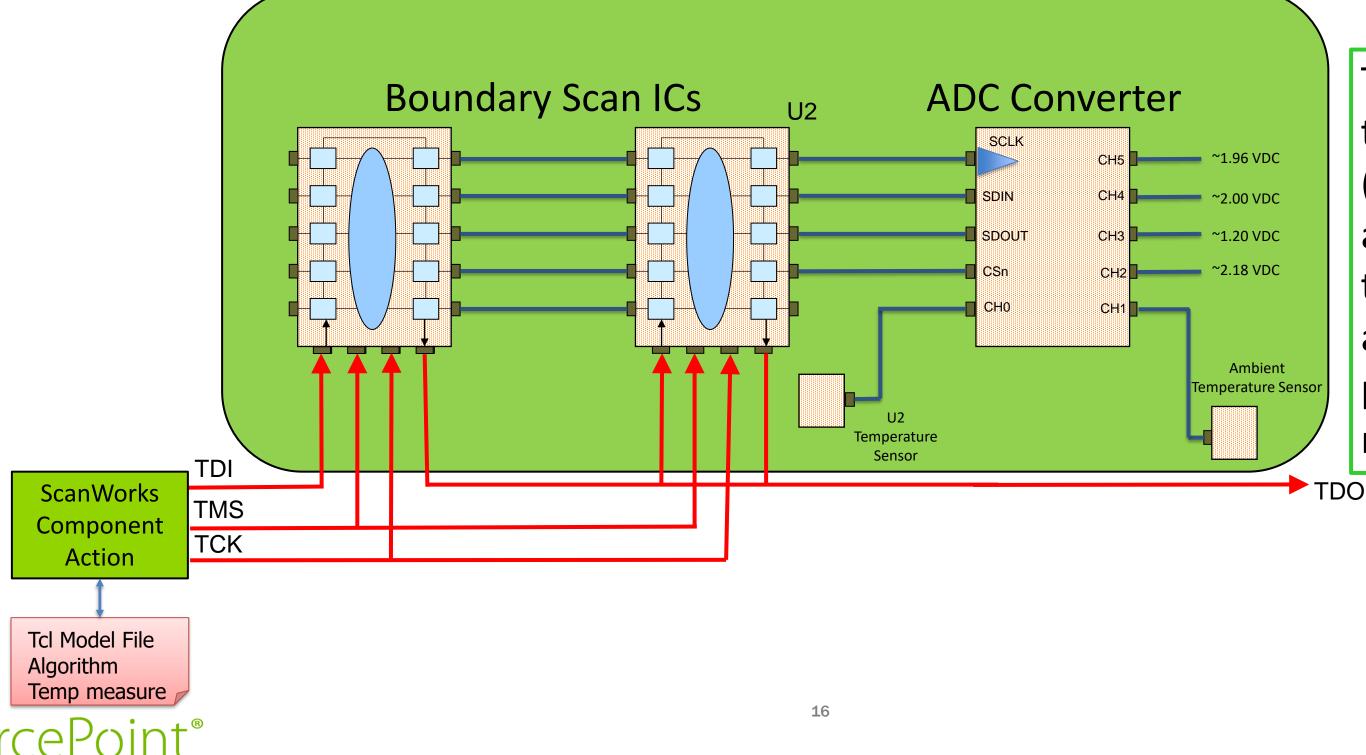

### **ADC with Temperature Measure**

Platform for Software Debug and Trace

© 2021, ASSET InterTech, Inc.

Test for device temperature (U2) vs. PCB ambient temperature along with power supply measurements

Platform for Embedded Ins

### Demonstration

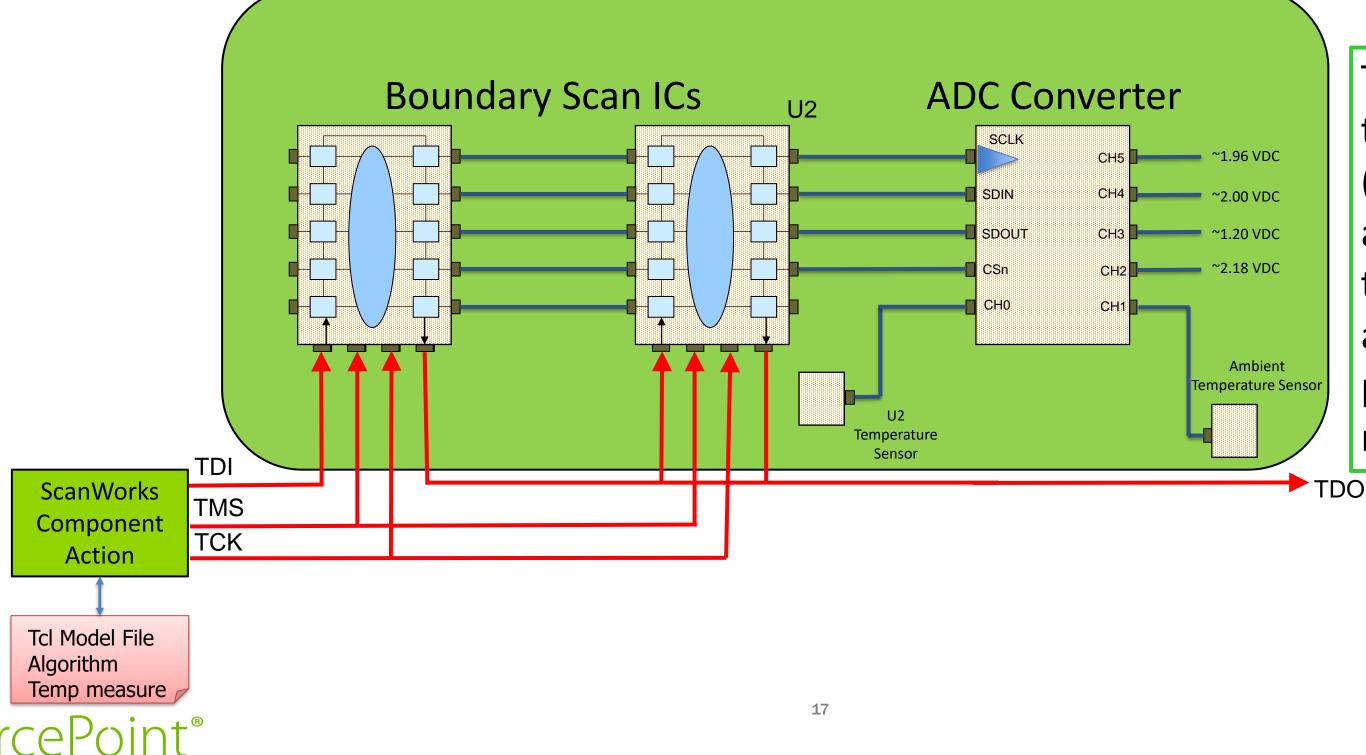

### **ADC with Temperature Measure**

Platform for Software Debug and Trace

© 2021, ASSET InterTech, Inc.

Test for device temperature (U2) vs. PCB ambient temperature along with power supply measurements

> Scan Platform for Embedded Inst

### Summary

- Bridging the boundary scan and functional test gap with the Component action has many positive results

- Adds functional testing to areas of the PCB that might have gone untested

- One station for structural, programming and functional testing reduces PCB handling and manufacturing cost

- Reduces need for large equipment saving factory floor space

- Failing devices can be identified during manufacturing where the cost to repair is lower as compared to latter production phases or at product release

- Functional test can be implemented through 3<sup>rd</sup> party applications such as LabVIEW, TestStand, along with boundary scan test

- ASSET provides a library of Component models for use as-is or as templates for model development so it's easy to get started

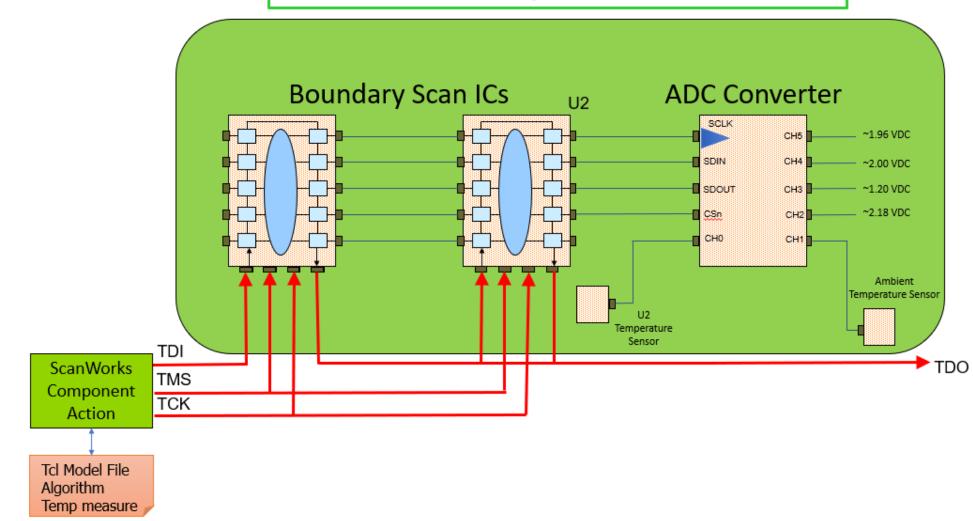

### ADC with Temperature Measure

ScanWorks®

## **For More Information**

- Go to our blog, Structural versus Functional Test, and Test Coverage versus Diagnostics, <u>https://www.asset-</u> intertech.com/resources/blog/2010/12/structural-versus-functionaltest/

- Download our eBook, Embedded JTAG for Boundary-Scan Test, https://www.asset-intertech.com/resources/eresources/embeddedjtag-boundary-scan-test/

- View our webinar, Onboard Fast Flash Programming Technology Innovations - Addressing Offboard Challenges, https://www.assetintertech.com/resources/videos/webinar-recording-onboard-fastflash-programming-technology-innovations-addressing-offboardchallenges/

### **Questions and Contact Information**

**Contact Information:** Michael R. Johnson 7161 Bishop Rd. Ste. 250 Plano, TX. 75024 mjohnson@asset-intertech.com www.asset-intertech.com

20

© 2021, ASSET InterTech, Inc.

# Real Insight from Code to Silicon

© 2021, ASSET InterTech, Inc.