ASSET’s Michael Johnson presented an update on Non-intrusive Board Test (NBT) at the 13th Annual Board Test Workshop (BTW) in Fort Collins, CO this past week. The overall question posed at the Workshop was, “Is Board Test Losing Relevance”?

The Board Test Workshop (BTW) is a pre-eminent workshop for board and system level test, including technologies such as 3D/2.5D test and SoC/NoC. It was started in 2001 and has been held almost annually ever since. The BTW attracts the thought leaders within Test Engineering from Contract Manufacturers, Test Equipment Providers, Researchers, Component/ Board/ System DFT Experts, System Providers and End Users.

The presentation agenda at this year’s Workshop was:

- SJTAG at BTW 2016, Scope, Purpose, Need, and Other Fun Stuff

- Board Test Standards and IC Design

- What’s New with IEEE 1149.6

- IEEE 1581: Ready for Primetime or the Sidelines

- An Update on Non-intrusive Board Test (NBT)

- PCB Board Warpage During In-Circuit Test (ICT)

- Simulation Based System-level Fault Insertion

- System Level, Ranked Reliability Based on Cost/Consequence

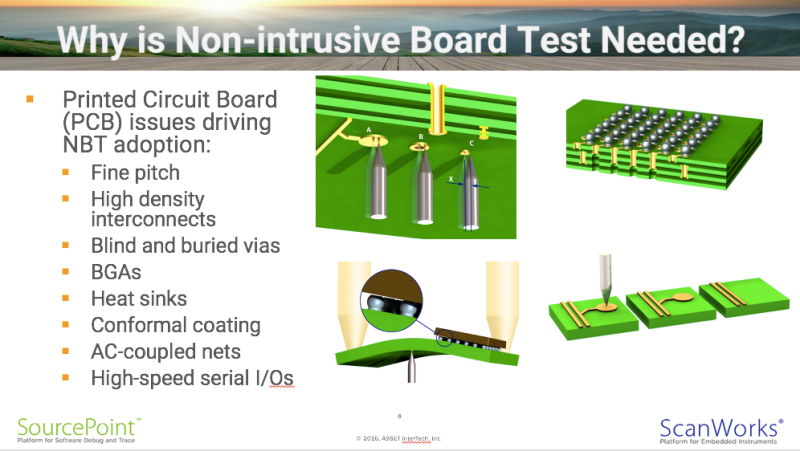

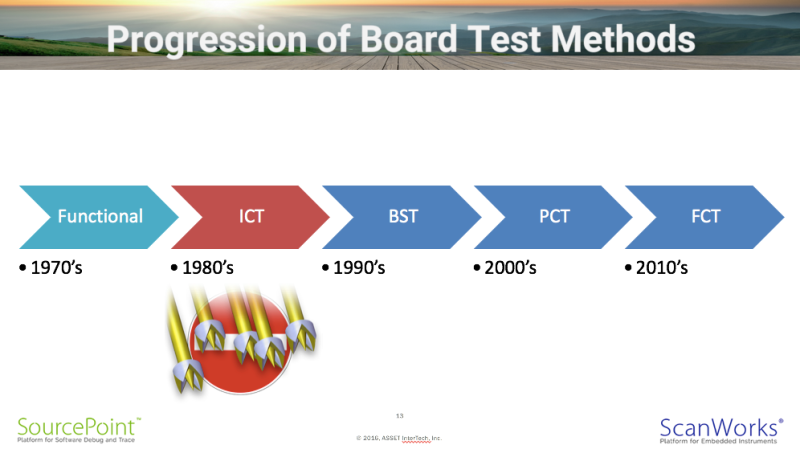

Michael Johnson, ASSET’s Product Manager for Boundary-Scan Test (BST) and FPGA-Controlled Test (FCT), delivered the NBT session. NBT denotes the generic class of technologies which do not use external physical test access (“bed-of-nails”); but rather, depends on silicon embedded instrumentation to perform the test function. His slides should be available (soon) on the BTW website. The essence of his presentation highlighted the struggle between board design and silicon design. PCB designers want chips with embedded instrumentation infrastructure that also functions correctly, whereas chip designers are concerned about implementing functionality within their devices, and embedded instrumentation test infrastructure is considered secondary. This is a major challenge due to diminishing external test access on today’s dense, complex designs; see the below visual for how traditional bed-of-nails access is become less viable.

Of course, using NBT instead of legacy intrusive board test technologies requires correctly designed embedded instrumentation, or Design-For-Test (DFT), infrastructure within the silicon. Boundary-Scan Test (BST, or sometimes referred to as JTAG) is one example of a component of NBT. See my blog here which describes how one silicon provider did not correctly provision BST within their device. Other components include Processor-Controlled Test (PCT) and FPGA-Controlled Test (FCT):

The overall consensus of the BTW was that Board Test is indeed not losing relevance; in fact, it is becoming more and more important over time. As margins for the Contract Manufacturers become even more razor-thin, there will be more and more emphasis on investing in new test technologies to provide a competitive cost edge. This does require that Test Engineers rise to the challenge of pushing their semiconductor suppliers to implement silicon embedded instrumentation properly, as well as convincing senior management of the ROI of NBT.