In my last article, I described how the Open Compute Project (OCP) Project Olympus server designs have been put into the public domain by Microsoft Azure. Inherent in the Olympus servers is the hardware connection between the ASPEED BMC and the CPU JTAG chain. To make the most of this connection for hardware-assisted debug and test purposes, a high-performance, secure JTAG Master function is needed within the BMC.

In the article Microsoft Project Olympus Schematics and Embedded JTAG Run-Control, I pointed out the schematic-level detail that supports embedded, JTAG hardware-assisted debug of Intel Xeon Scalable Processor (formerly termed Purley, or Skylake-EP) based servers. Therein, the ASPEED BMC acts as a debug master, using the JTAG state machine, JTAG Test Access Port (TAP) pins, and sideband GPIO signals to activate and respond to the Design for Debug (DfD) facilities inside the Intel silicon. The same topology applies to AMD EPYC, Cavium ThunderX2, and presumably Qualcomm Centriq-2400 based designs.

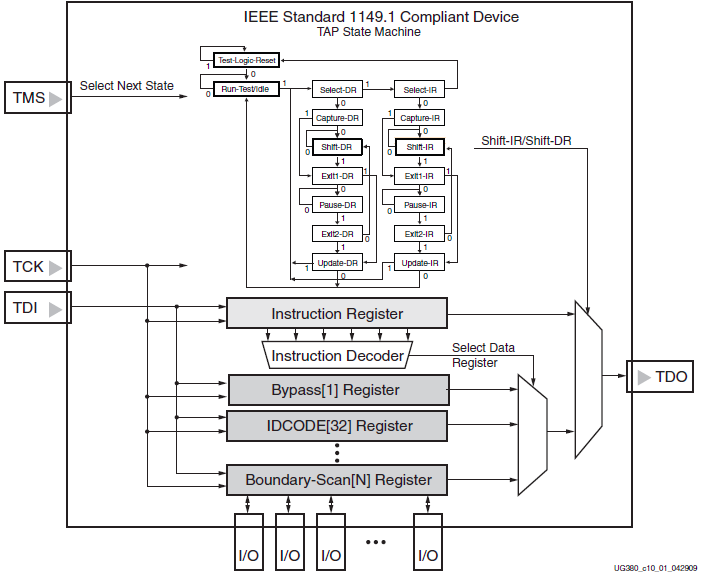

BMCs may operate in either of two modes for performing the JTAG mastering function: what are commonly called software mode or hardware mode. Software mode is basically “bit-banging” or “pin-wiggling”, wherein the BMC is made to cycle one TCLK period while driving values on TDI and TMS and returning the value of TDO. BMCs without a dedicated JTAG hardware master burned into their silicon will use software mode, at the cost of poor performance (typically 1-2 MHz sustained TCK, which is suitable for slower applications like test, but unsuitable for debug forensics functions that retrieve a lot of data). JTAG hardware mode acts as an accelerated version of the software mode, by having the JTAG state machine functions in silicon logic, and batching up scans (as from the Xilinx Spartan 6 Configuration Guide):

It’s not unusual to have hardware mode operate 10X – 20X or more faster than software mode.

ASSET, being a JTAG company, has of course deep expertise in the technology behind JTAG and run-control. The JTAG Mastering function is built within each of our boundary-scan test (ScanWorks) product controllers, and our hardware-assisted debug and trace (SourcePoint) controllers. We license the intellectual property (IP) behind our JTAG Master to 3rd-party companies that have need of this technology.

On any given design, the ASSET JTAG Master RTL, presents to higher-level functions a simple VHDL port that behaves like a standard Wishbone slave. Alternative ports, such as one that has SRAM-like behavior, are also offered.

The JTAG Master API, written in ‘C’, implements the support for operations such as state move, scan IR, RunTCK, ScanTest, and others. For example, a subset of function classes (TAP navigation, general scans, alternative scans, ASP scans, end state control, etc.) is shown in the following table:

|

Class |

Feature |

Desired Behavior |

|

TAP navigation |

state move |

The ability to move to any of the stable states within the TAP state diagram upon request. |

|

General scans |

scan DR |

The ability to perform DR scans of any bit length. |

|

Alternative scans |

scan NoRTI |

The ability to operate succcessive DR scans (capture, shift, update) without passing through Run-Test Idle (RTI) state. Identical to scan DR except that scans starting in Pause-DR will update and capture without going through RTI. |

|

ASP scans |

scan noTMS |

The ability to scan information while in Run-Test Idle, Pause-DR, or Pause-IR. No TMS activity should occur. |

|

End state control |

Enddr | endir |

The ability to define the stable state the JTAG Master will navigate to after it has completed a scan. |

|

TCK control |

(hybrid tck) |

The ability to operate the TCK as a free-running clock except, ONLY, in the case of scan buffer stall. |

Why is this important? Implementing hardware-based engines correctly within silicon, and having the associated driver and library support, provides optimal performance and reliability for debug and test applications. You can read more about how the JTAG mastering function is used for debug in our technical brief, ScanWorks Embedded Diagnostics. The description of test applications can be read about in our eBook, Embedded JTAG for Boundary-Scan Test.