In my last blog, I introduced the three types of JTAG access for debug applications. This article delves into the third type, Embedded ITP.

In the blog The Three Types of JTAG Access on Intel-based Designs, a brief introduction was given to XDP, DCI/USB3, and Embedded ITP. The latter two types progressively provide more and better access for “closed chassis” systems – that is, for systems which are sealed in a chassis or frame, or otherwise inaccessible to legacy XDP. XDP (short for eXtended Debug Port) provides JTAG access over a proprietary 60-pin connector on the motherboard, which might be obstructed or removed. DCI/USB3 allows debug access over an appropriately enabled USB3 port on the target.

Both XDP and DCI/USB3 suffer from the constraint of requiring physical access to the target: that is, there must be a physical connection between the target debug interface (either the XDP connector or the DCI/USB3 port) and the hardware probe hosting Intel In-Target Probe (ITP) debug functionality. Embedded ITP removes this restriction. By embedding the ITP debug engine within a BMC or other service processor on the design, the BMC can emulate the hardware probe, eliminating it. And since most BMCs provide out-of-band Ethernet access out of the target as part of their service management functions, debug results data can be offloaded from the platform over TCP/IP without any protocol conversions.

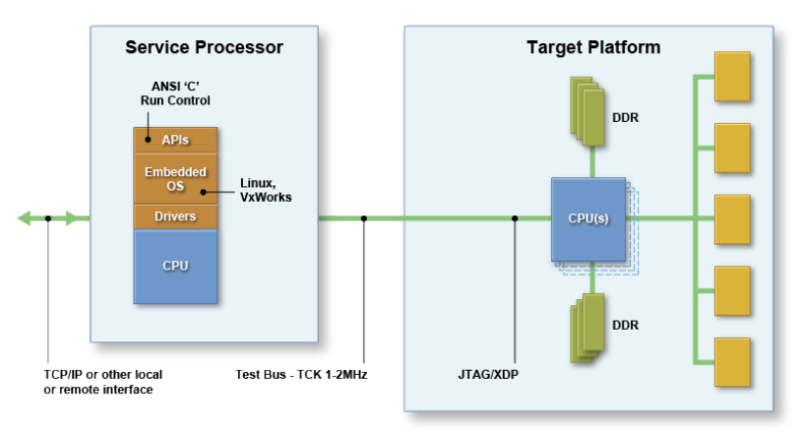

A graphic of the Embedded ITP topology is as follows:

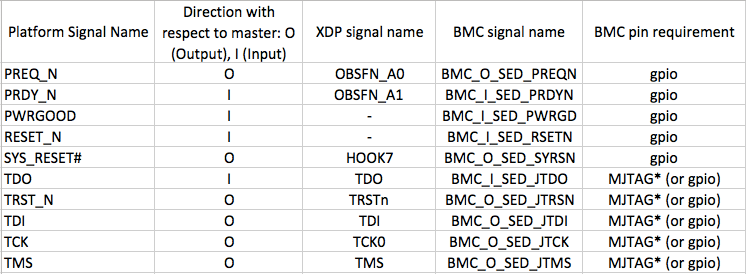

The question arises as to the requisite signals needed to interface between the Embedded ITP service processor host, and the target. Much of this information can be gleaned from public Intel resources such as the Debug Port Design Guide for UP/DP Systems and Debug Operations User Guide for Intel® Quark™ SoC X1000, for example. A summary of a minimum set of requisite signals is in the following table:

* NOTE: MJTAG indicates that the BMC implements an available JTAG Master function, such as the Emulex Pilot4. This boosts performance significantly.

Should there be any constraints in terms of GPIO access, it is possible to work with smaller access signal configurations. And more advanced debug scenarios may add additional signal requirements. If you would like to know more, drop me a Comment below. More technical information on Embedded ITP (we call it ScanWorks Embedded Diagnostics, or SED for short) is available here.