Part 1 of a three-part blog

To date, 3D chips have been fabricated in a number of ways, including stacking packages, flip chips, bonded bare die and others. Their names also tend toward the exotic, like PoP (package-on-package), PiP (package-in-package) and SiP (system-in-package). Now, a new methodology has emerged involving directly stacking wafers or die and connecting them with through-silicon-vias (TSV).

The majority of today’s 3D chips with TSVs feature interposers and are correctly referred to as 2.5D chips. Soon though, true 3D chips with TSV will reach volume manufacturing because a great deal has been invested in R&D and many different formulations of test chips have been investigated. One problem that still remains is how to test true 3D chips with TSV. JTAG or IEEE 1149.1 boundary-scan as well as IEEE 1687 Internal JTAG (IJTAG) could provide the basis for a solution.

Right now there just is no easy way to verify that the TSV connections, which can be as many as 10,000 tiny bumps, are complete, good, and successful because they are sandwiched between silicon die. Unlike a nonfunctional chip on a circuit board which can be removed from the board or from a socket on the board, a stacked 3D chip cannot be unstacked. The current thinking on this problem is that a boundary-scan (IEEE 1149.1 JTAG) type of function on each die could perform interconnect tests on the digital TSVs connecting the die. To do this, the IEEE 1149.1/JTAG infrastructure or a subset of it must be present on each die and the test infrastructure on each die must be connected together to enable a test method for the entire system. Developing this concept is the scope of the IEEE P1838 3D Test Standard’s working group.

A lot of work has already been done on the IEEE P1838 standard. Much of that work has been the basic setting of objectives, conceptualizing and defining terminology so that all of us on the working group understand what we mean when we think we are talking about the same thing. As Erik Jan Marinissen, the chairman of the group says, “All noses are pointing in the same direction”.

The key points for 3D test are:

1) A test architecture is needed for each die in a stack. Prior to stacking, each die should be self-contained and testable. This will allow a die to be seamlessly included into a stack so that its test features can to be combined with the test features of the other die in the stack. Specifically, the test capabilities on each die should interface with each other identically. In other words, the data and control pins to operate the test features should be the same on each die.

2) Each die should support an IEEE 1149.1 Test Access Port (TAP) and TAP controller as the preferred test interface. At the very least, this will create a serial scan path for accessing the test and debug functionality on each die and extend this access to the next die.

3) Each die’s serial scan path must allow access upward to the die above it and downward to the die below it. Not all die in a stack must be active at all times during testing.

4) If a die in a stack is not on the active scan path, it should be parked offline for power, quiescence, safety and security reasons.

5) The access method should allow an ACTIVATE command for a die so it can be turned on and accessed. In other words, a die that is parked must be enabled before it is accessed. ACTIVATE for a die may be enabled in both the upward or downward directions.

6) If a die is in the active scan path but it isn’t being tested or participating in a test function, it should have minimum impact on the scan path. For example, a single bit bypass register might suffice.

7) Each die should have a unique identification code so that it is identifiable in the stack.

8) Each die should have an interface boundary register upward to the die above and another interface boundary register downward to the die below. Whether each direction should be accessible separately, such as an EXTEST-UP and an EXTEST-DOWN, is still being investigated. Note that the lower surface in a 3D stack of die is called the Primary Interface while the upper surface is referred to as the Secondary Interface.

Chip Test

Testing a die is the same as testing what is today called a chip, but without the package. The problem with testing a die involves access since a conducting probe only has access through the small bumps on the bottom of the die. Some experts think that several methods will allow probe testing of a die to create known-good-die (KGD). Another alternative is IEEE 1149.1 JTAG and the IEEE 1687 IJTAG on-die architecture, which will provide access to test and debug instruments in the die. Since this is not very different from simply using the IEEE 1149.1, IEEE 1500 or IEEE 1687 standards as they are today, this is not within the scope of the IEEE P1838 working group to define or standardize. The working group is not re-defining the IEEE 1149.1 JTAG TAP controller and its instruction set to serve the purposes of 3D chip test.

Board Test

Two aspects of circuit board test need to be investigated with regards to testing the design of a 3D chip. One aspect is how the completed packaged 3D stack will interact with the board where it will be soldered onto or placed into a socket. Of course, compliance with the IEEE 1149.1 boundary-scan standard must be maintained. This would mean including items such as support for all four mandatory JTAG pins that comprise the TAP, support for the IEEE 1149.1 finite state machine, defining the reaction to the application of five logic ones on TMS (the TAP controller resolves to reset TLR state), and defining how to minimize the scan path (TDI to TDO) to a single bypass bit with a BYPASS instruction.

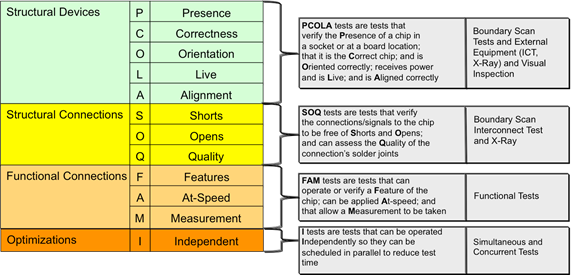

However, a 3D die stack closely resembles a circuit board in a package. As a result, the configuration and operations of test features for this complex stack of die falls within the realm of test and debug capabilities for a board. Board designs are not evaluated against stuck-faults, delay-faults or gate-faults the way that chips are. Instead, boards are evaluated against a methodology known as PCOLA, which has been defined by the International Electronics Manufacturing Initiative (iNEMI). Here’s a recent blog on PCOLA by one of my colleagues at ASSET and the table below explains what each letter in PCOLA stands for.

PCOLA assumes that each chip on a board has been tested and found to be a good chip. PCOLA is only concerned with verifying or testing the board. The term PCOLA is actually shorthand for referring to PCOLA/SOQ/FAM which represents the entire methodology as defined in the figure above. Most of the aspects of PCOLA are fairly self-explanatory, except for FAM, which refers to whether the board can support the functional (specification) behavior, perform at-speed and can a measurement be taken.

The next two articles will investigate the current solution for stackable memory die and the expansion and application of PCOLA for 3D chips.

NOTE: Al Crouch is a member of ASSET’s consultation team. If you think Al’s expertise would be helpful to you, click here for more information.