Is it possible to bend, but not break, some time-honored board design guidelines to reduce board cost, but still maintain signal integrity?

In my last couple of blogs, I covered how PCB insertion loss increases with higher signal frequencies, and how this affects signal integrity negatively. At some point, channel margins begin to collapse, with greatly lowered system stability. It is possible to address this by adding to PCB cost: designing with wider traces, providing for looser coupling between differential pair, using thicker dielectrics or more exotic materials.

Clever design practices can mitigate this and keep PCB cost under control. For example, in Single Stripline versus Dual Stripline, and Board Routing, we saw how using dual striplines can allow for more highly dense board form factors via a reduced number of layers.

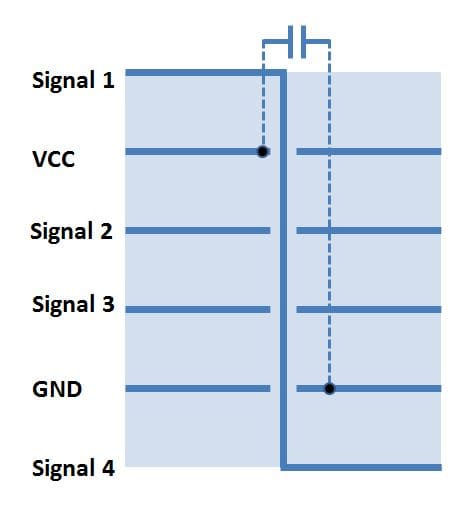

Another way to keep PCB cost under control is to carefully examine some time-honored board design guidelines, and see how they might be “bent”. For example, common design practice is to employ reference plane stitching vias or decoupling capacitors whenever high-speed signals need to transition layers. This is because there must be a return current path for each signal, and this current must be returned on an adjacent power or ground plane.

If the two such planes are at the same potential, a stitching via is sufficient. If they are not at the same potential, a decoupling capacitor provides the low-impedance pathway.

The problem with stitching vias and decoupling capacitors is that they add to routing complexity and take up much board area – often adding extra layers to dense designs. But for differential signals, if care is taken, such vias and caps can be left out, and the design may still have sufficient margin. We’ll cover the physics behind this in a future blog.

Of course, diverging from standard design practices creates risk, only some of which can be mitigated through simulation. The importance of actual margin measurements on board designs is covered in our white paper, System Marginality Validation of DDR3 | DDR4 Memory and High-Speed I/O.