Poorly tuned adaptive equalization will cause systems to

gulp power, instead of sipping it. What’s the technology behind this?

In two previous blogs, I described the nature of adaptive equalization, and also explained how programmable

and adaptive equalizers complement each other. An example of the former would be

CTLE (Continuous Time Linear Equalization), and of the latter, DFE

(Decision-Feedback Equalization). Adaptive equalization becomes very important at

higher bus speeds, where signals are corrupted by higher attenuation,

reflections, coupling, and noise from chip and board variances – such signals

requiring “reconstruction” in order to provide acceptable operating margins and

for a circuit board to thus work properly. Except for systems with the lowest

requirements for power and size, adaptive equalization is standard for anything

above 5Gbps. For example, DFE is provided on Intel® QuickPath Interconnect

(QPI) and PCI Express (PCIe) Gen3 buses. Adaptive equalization continually

adjusts itself to the unique characteristics of each combination of chips,

boards, and variances thereof.

The problem with adaptive equalization is power consumption.

DFE, for example, can add anywhere from 15% to 30% of the overall SerDes power

for an optimized PCIe design[i]. At

the 40nm process node, a general industry rule is that DFE requires 5mW per

Gbps of data per each DFE TAP; so a standard 5-TAP implementation requires 250

mW/channel at 10Gbps[ii].

At 28nm, if we estimate total SerDes power consumption to be 120mW per full

duplex channel at 8Gbps[iii],

we see that DFE for a single x16 PCIe Gen3 port can consume about half a watt.

On a given high-end design, which will have dozens and dozens of channels,

adaptive equalization can easily consume 5W- 10W or more.

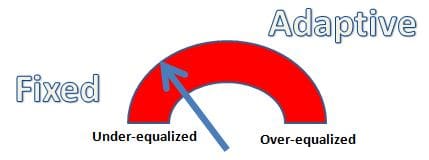

So, tuning adaptive equalization is extremely important to

reduce overall power utilization. This involves striking a balance between

fixed and adaptive equalization so that the adaptive logic is not doing too

much work. For example, if a link is under-equalized, the fixed equalization

settings (set in the BIOS or boot loader) are too low, and the adaptive

equalization carries more of the burden. Not only does this consume more power,

but typically it “strains” the DFE at the extreme of its operating region,

yielding poorer margins on lanes that are on the edge of the guard band. This

can be visually represented below:

The ‘5×5’ methodology to perform tuning of fixed and

adaptive equalization on Intel Xeon platforms can be read here: http://www.asset-intertech.com/Products/High-Speed-I-O-Validation/HSIO-Software/HSIO-Application-Brief.