# Contents

| Revision History              | 5  |

|-------------------------------|----|

| Introduction and Code Samples | 6  |

| ai_ErrorToString              | 15 |

| ai_GetLibraryVersion          | 16 |

| ai_mBasicRWRamTest            | 17 |

| ai_mBootRomBusTest            | 20 |

| ai_mCheckMemory               | 22 |

| ai_mClose                     | 25 |

| ai_mConfig                    | 26 |

| ai_mCPUID                     | 28 |

| ai_mDownloadUserDiag          |    |

| ai_mDRamRefreshTest           |    |

| ai_mEnableoxmdebug            |    |

| ai_mEnableRAMAreaasCAR        |    |

| ai_mEnableUUTDiagsAreaasCAR   | 40 |

| ai_mEnterDebugMode            | 42 |

| ai_mExecuteUserDiag           | 44 |

| ai_mExitDebugMode             | 47 |

| ai_mFillMemory                | 49 |

| ai_mFXRSTOR                   | 52 |

| ai_mFXSAVE                    | 54 |

| ai_mGetActiveCore             | 56 |

| ai_mGetActiveCPU              | 57 |

| ai_mGetActiveThread           | 58 |

| ai_mGetBreakpoint             | 59 |

| ai_mGetDebugModeStatus        | 61 |

| ai_mGetITPScanChainTopology   | 63 |

| ai_mGetPriorStateInfo         | 66 |

| ai_mIOSFcrashdumpDiscovery    | 68 |

| ai_mIOSFcrashdumpGetFrame     | 69 |

| ai_mIOSFreadEndpointConfig    | 70 |

| ai_mIOSFreadMSR                 | 71 |

|---------------------------------|----|

| ai_mIOSFreadPCIConfig           | 72 |

| ai_mIOSFreadPCIConfigLocal      | 73 |

| ai_mIOSFreadPkgConfig           | 74 |

| ai_mlOSFTAPinit                 | 75 |

| ai_mlOSFTAPownership            | 76 |

| ai_mIOSFwritePCIConfig          | 77 |

| ai_mIOSFwritePCIConfigLocal     |    |

| ai_mIOSFwritePkgConfig          | 79 |

| ai_mlsPowerOn                   | 80 |

| ai_mNavigatetoTAPState          |    |

| ai_mOpen                        | 82 |

| ai_mOpenEx                      |    |

| ai_mRamBusTest                  |    |

| ai_mRamBusTestChannel           |    |

| ai_mRamBusTestviaFIFO           | 92 |

| ai_mReadCR                      | 95 |

| ai_mReadCSR                     | 97 |

| ai_mReadDescriptorTableRegister |    |

| ai_mReadDR                      |    |

| ai_mReadGPR                     |    |

| ai_mReadIO                      |    |

| ai_mReadMemory                  |    |

| ai_mReadMSR                     |    |

| ai_mReadSegmentRegister         |    |

| ai_mResetDetect                 |    |

| ai_mResetUUT                    |    |

| ai_mReturnIDCode                |    |

| ai_mReturnIDCodewithOverscan    |    |

| ai_mReturnSiliconID             |    |

| ai_mRomCrcTest                  |    |

| ai_mRunUUT                      |    |

| ai_mRWRamTest                   |    |

|                                 |    |

| ai_mScanDr                       | 127 |

|----------------------------------|-----|

| ai_mScanIr                       | 130 |

| ai_mSetActiveCore                | 132 |

| ai_mSetActiveCPU                 | 133 |

| ai_mSetActiveThread              | 135 |

| ai_mSetBreakpoint                | 136 |

| ai_mSetDebugModeCheckFlag        | 138 |

| ai_mSetinitbreak                 | 139 |

| ai_mSetmachinecheckbreak         | 141 |

| ai_mSetRunMode                   | 143 |

| ai_mSetshutdownbreak             | 145 |

| ai_mSetsmmentrybreak             | 147 |

| ai_mSetTap                       | 149 |

| ai_mSetTargetCPUType             | 150 |

| ai_mStopTest                     | 152 |

| ai_muregraw                      | 153 |

| ai_muregraw64                    | 154 |

| ai_mWaitforDebugMode             | 157 |

| ai_mWBINVD                       | 159 |

| ai_mWriteCR                      | 161 |

| ai_mWriteCSR                     | 163 |

| ai_mWriteDescriptorTableRegister | 165 |

| ai_mWriteDR                      | 167 |

| ai_mWriteGPR                     | 169 |

| ai_mWritelO                      | 171 |

| ai_mWriteMemory                  | 173 |

| ai_mWriteMSR                     | 175 |

| ai_mWriteSegmentRegister         | 177 |

# Revision History

| Revision Number | Description                                                      | Date               |

|-----------------|------------------------------------------------------------------|--------------------|

| 2.01            | - Removed NDA requirement, retained Copyright                    | September 26, 2021 |

| 2.00            | - Sapphire Rapids support                                        | September 7, 2021  |

|                 | - CheckValue parameter added to                                  |                    |

|                 | ai_mCheckMemory()                                                |                    |

|                 | <ul> <li>- ai_mGetBreakPoint() BreakPointNo parameter</li> </ul> |                    |

|                 | should be uint8_t* and not uint8_t                               |                    |

|                 | - ai_mGetITPScanChainTopology:                                   |                    |

|                 | ai_CoreTopology_t core[24] should be core[60]                    |                    |

| 1.00            | Original document                                                | March 25, 2021     |

## Introduction and Code Samples

Welcome to our API Reference Manual! We hope that you find the contents useful and interesting. If at any time you have any feedback or questions, feel free to reach out to us at <u>ai-info@asset-</u><u>intertech.com</u>, or use our handy Contact Us form at <u>https://www.asset-intertech.com/contact-us/</u>.

This API Reference Manual provides an alphabetical listing of all interfaces available within the ScanWorks Embedded Diagnostics (SED) run-control library. It is ASSET's intent to keep the library and documentation current, universal, and backwards compatible as of the most recent supported x86 platforms. As of the time of this writing, the current supported Intel CPU/platform is Sapphire Rapids/Eagle Stream, and the library and documentation support all the way back to the Intel Nehalem platform.

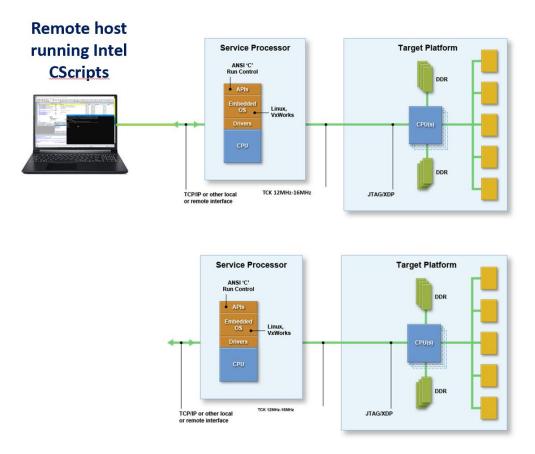

The two major use cases for the SED API are (1) remote CScripts application, and (2) On-Target Diagnostics (OTD). You can see this from the below diagram:

Figure 1: Remote CScripts, and On-Target Diagnostics

At the top, the remote host PC, running Windows or Linux, communicates over Ethernet or other transport with the BMC, that hosts the run-control library and the JTAG driver and mastering function.

At the bottom is the main topic of this Reference Manual: the BMC is autonomous, and executes applications written in C/C++ as OTDs. We'll describe the general approach involved in using the SED library, and then walk through individual code samples to show how it's used.

Note: in this Reference Manual, although we strive to write efficient code and follow best SED programming practices, the main goal of each sample program is to demonstrate SED concepts or programming techniques. Writing the most optimal code was not the goal, and would likely obfuscate the ideas trying to be illustrated. Keep this in mind if you are using any of the sample code in your own projects, as you may wish to rework it for better efficiency. Moreover, in order to focus on the SED API, we have built minimal infrastructure on top of it. This means the illustrative software sometimes hardcodes values and define things in the source code that might normally be data driven.

We will illustrate the main functionality of the SED API by using a program called "ltloop". ltloop is an application that stresses PCI Express ports by exercising the Link Training & Status State Machine (LTSSM) on upstream and downstream PCI Express devices, looking for device, firmware and board marginalities. If you're unfamiliar with the LTSSM, please review some background reading such as <u>Built-In Self Test (BIST) for PCI Express using Embedded Run-Control</u> and <u>What is Surprise Link Down (SLD)?</u> We won't delve into the detailed nature of this application here, other than to use it for illustrative purposes for the API. Note that this example works on an Ice Lake server platform.

The source code for ltloop is here: Download ItloopExample.

Let's firstly start off by looking at main():

```

int main (int argc, char **argv)

int numcores;

int curcore;

int curcore;

int curcore;

int iter = 0;

bool pwrchk = true, sensetup = true, savemodarch = true;

int mHandle;

FILE *UUTDiagsHexFile;

char ver[200];

uint64_t mar;

uint64_t mar;

struct timespec start_time;

struct timespec end_time;

double secs;

uint32_t dev;

uint32_t dev;

uint32_t fun;

a_ ITPtopology t topo;

uint16_t curcPU;

UUTDiagsHexFile = NULL;

printf("\n\nLink Training Loop test\n");

iError = parseArgs(argc, argv);

if (iError != 0)

{

usage();

return iError;

}

ai_CetLibraryVersion(ver);

printf("Library version = %s\n", ver);

AI_pdoselector pdctarget = AI_pdc_0;

if ((iError = ai_mOpen(pdctarget, 1, $mHandle)) != AI_SUCCESS)

```

© 2021 ASSET InterTech, Inc.

#### Introduction and Code Samples

```

\nOpen ERROR: %s Channel %i\n" , ai_ErrorToString(iError), pdctarget);

m bus 0 = 0;

ai mSetActiveCore(mHandle, CORE_ZERO_POS);

```

© 2021 ASSET InterTech, Inc.

Most OTDs have the same structure within the main routine. The platform is initialized for run-control with the following API, in sequential order:

The operation of these functions should be made fairly clear by looking at the source code. Here are some examples.

The invocation of ai\_mOpen is in line 1255:

#### if ((iError = ai\_mOpen(pdctarget, 1, &mHandle)) != AI\_SUCCESS)

Since the third argument is &mHandle, the value of mHandle can be updated within this function. mHandle is a unique identifier connection to a specific PdcNo – which in turns relates to the number of CPUs that the service processor JTAG Master is intended to drive. In this case, it's left at the default of AI PDC 0; the default of one chain or node.

The invocation of ai\_mSetActiveCPU is in line 1286:

if ((iError = ai\_mSetActiveCPU(mHandle, curCPU)) != AI\_SUCCESS)

while iterating across the values of curCPU (normally two in a 2-socket system, four in a 4-socket system, etc.).

And ai\_mEnterDebugMode is in line 1294:

if ((iError = ai\_mEnterDebugMode(mHandle)) != AI\_SUCCESS)

This function forces all connected CPU cores of the node identified by mHandle in to debug mode. Said another way, they enter probe mode, and are then available for other run-control operations. Debug mode or probe mode is a state in which the platform must be to execute many of the SED library

functions; though this is not true in all cases, which will be shown when we discuss the Intel On-chip System Fabric (IOSF) related functions, such as invoked in ai\_mIOSFTAPinit (mHandle) on line 1303. But, let's skip ahead of these calls for now.

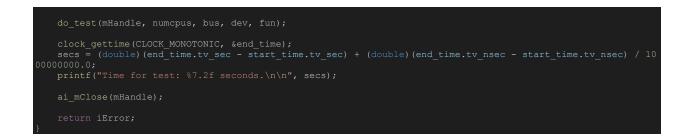

After the platform probe mode initialization is complete, the flow of the program is as follows:

prepTarget(mHandle, 0, 0, 0); getBusNumbers(mHandle, curCPU); port2bdf(m\_port, &bus, &dev, &fun); do\_test(mHandle, numcpus, bus, dev, fun); lt\_loop(mHandle, bus, dev, fun);

After the main platform initialization is done, ltloop does some specific work to provide sideband (i.e. not run-control based) access with the IOSF routines in main (). Although there are references to PECI in the code, in this instance JTAG is still used as the physical access mechanism to the meta state machine, but not run-control. Then port2bdf is called (a handy utility function to translate the port number from the command line to bus/ device/ function). Finally do\_test is launched, which in turn launches the lt\_loop function, where all the heavy lifting is done.

Let's first look at the parseArgs(argc, argv) function called initially within main() to see the overall parameters and operations supported by the Itloop OTD:

```

int parseArgs(int argc, char **argv)

int c;

int retval = 0;

while ((c = getopt (argc, argv, "l:p:t:s:f:cdbo?h")) != -1)

{

switch(c)

{

case 'p':

//printf("Option p: %s\n", optarg);

m_port = atoi(optarg);

if ((m_port < 0) || (m_port >= MAXPORT))

{

printf("Invalid port value: %d \n", m_port);

retval = -1;

m_port = 0;

}

break;

case '1':

m_loops = atoi(optarg);

if (m_loops < 1)

{

printf("Invalid number of loops, must be > 0.\n");

retval = -1;

m_loops = 1;

}

break;

case 's':

m_socket = atoi(optarg);

//Will check socket # in main after we get system topology and learn # of CPUs

break;

case 't':

m_type = atoi(optarg);

//Will check socket # in main after we get system topology and learn # of CPUs

break;

case 't':

m_type = atoi(optarg);

//Will check socket # in main after we get system topology and learn # of CPUs

break;

case 't':

m_type = atoi(optarg);

//Will check socket # in main after we get system topology and learn # of CPUs

break;

case 't':

m_type = atoi(optarg);

//Will check socket # in main after we get system topology and learn # of CPUs

break;

case 't':

m_type = atoi(optarg);

//Will check socket # in main after we get system topology and learn # of CPUs

break;

case 't':

m_type = atoi(optarg);

//Will check socket # in main after we get system topology and learn # of CPUs

break;

case 't':

m_type = atoi(optarg);

//Will check socket # in main after we get system topology and learn # of CPUs

break;

case 't':

m_type = atoi(optarg);

//Will check socket # in main after we get system topology and learn # of CPUs

break;

case 't':

```

© 2021 ASSET InterTech, Inc.

```

m_type = 1;

retval = -1;

ai mIOSFdebugPrint(true);

m forceSpeed = atoi(optarg);

if ((m_forceSpeed > 4) || (m_forceSpeed < 1))

m pciScan = true;

if ((m_port == 0) && (m readDSC))

m readDSC = false;

```

You can see that the switch on the input parameters (i.e. we might invoke Itloop via "Itloop -s1 -p5 -t1 - I10000") gives us the following options:

"s" : socket number

"p": PCIe port number

"I" : the number of LTSSM loop tests to run; for example, how many retrains to do

"t" : Test type. Only 1 and 6 are supported in this routine. "1" is a simple link retrain test, and "6" is a speed change loop test (i.e. from Gen1 to Gen4 and back).

"d" : this provides the option to conduct testing on the downstream device (DSC – downstream component) as well as the upstream component. The default is "false" to optimize for time. But we can set it to "true" to have the test be more rigorous.

"b" : This allows for debug information to be sent from when we use the IOSF to access the PCI Express configuration registers. It's a debug utility, mostly for use by ASSET or Intel personnel to do some troubleshooting if needed.

"o" : Another debug utility, just to do a subset equivalent of the "sysTopo" CScript. This overrides all other options.

"f" : Forces the port to a given speed; for example, Gen1, Gen2, Gen3, Gen4.

"c" : Does a scan and a print of all B/D/F.

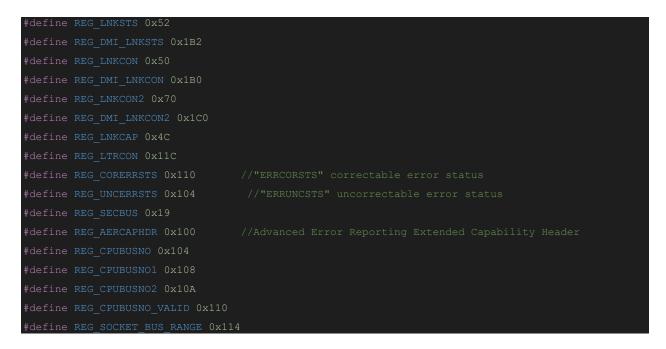

Much of the "heavy lifting" happens in the lt\_loop(int mHandle, uint32\_t bus,

uint32\_t device, uint32\_t function) routine. Note that it makes use of some of the key

register definitions as defined early in the program:

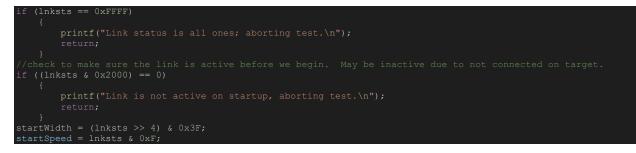

The PCIe register definitions such as REG\_LNKSTS are found in the Intel EDS; but, in lieu of that, a lot of the underlying methodology is common to all x86 platforms and in the public domain, such as here: <a href="https://www.intel.com/content/dam/www/public/us/en/documents/datasheets/atom-processor-s1200-datasheet-vol-2.pdf">https://www.intel.com/content/dam/www/public/us/en/documents/datasheets/atom-processor-s1200-datasheet-vol-2.pdf</a>. Note that lnksts has been renamed to linksts, but we keep the old legacy LNKSTS here. lnksts is at offset 0x52 and contains useful information such as whether link training is complete or in progress, what the link width is, whether it's up or not, and the link speed. We see later that we read its contents with the call at line 621:

lnksts = readRegisterPeci(mHandle, bus, dev, fun, reg lnksts, AI bw16);

and then we do some compares, status checking, and place the link width and speed in our local variables:

Note at the top that we retrieve lnksts using the function readRegisterPeci as opposed to a standard JTAG/MMIO read. This routine does not use PECI as an access mechanism; rather, it uses the sideband IOSF access mechanism as a means to not halt the target. So, despite the name, it's still JTAG. The end result is the same, though: we retrieve all 16 bits of LNKSTS, do the "and" with bit 13 to see if the Data Link Control and Management State Machine is in the DL\_Active state, and if so we get the Negotiated Link Width by shifting right four bits and ANDing with x3F, thereby isolating the bits 9:4 which contains the width. We also assign startSpeed to the last four bits.

Next we do the same thing with lnkcon (in the EDS, this has been renamed to linkctl):

```

lnkcon = readRegisterPeci(mHandle, bus, dev, fun, reg_lnkcon, AI_bw16);\

lnkcon = lnkcon | 0x20; //set the retrain link bit

```

Note that we set bit 5 of lnkcon, via the OR with x20, to initiate the link retrain. We then later use runcontrol (not IOSF) to fire off the retrain:

```

//Write the LNKCON register to cause the link to retrain

writeRegisterMem(mHandle, membus, dev, fun, reg lnkcon, AI bw16, lnkcon);

```

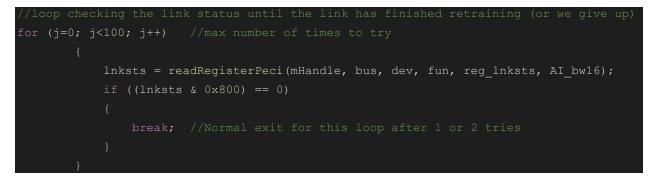

We then iteratively loop for up to 100 times (normally it only takes one or two loops), checking the link retrain bit, to see if the retrain succeeded:

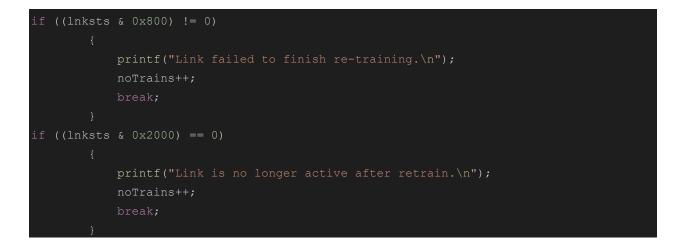

And afterwards we check that the Link Training bit (bit 11 of lnksts, the result of the mask with 0x800) should be zero, and that we're in the DL\_Active state (via the mask with 0x2000, bit 13). Otherwise, we bail.

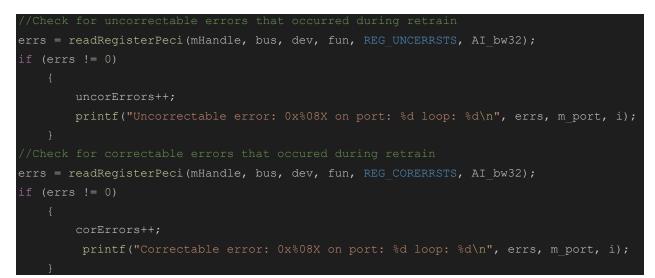

Finally, as an example, we collect the number of correctable and uncorrectable errors while we're in the loop:

And that's it! Hopefully you've found this helpful in creating your own OTDs.

### ai\_ErrorToString

## NAME

## ai\_ErrorToString

Converts an integer error code to a string.

## **SYNOPSIS**

#include <itp\_driver.h>

const char \*ai ErrorToString(int rval);

## DESCRIPTION

ai\_ErrorToString() takes the integer error code rval and returns the associated character array of error information.

## **RETURN VALUE**

The ai\_ErrorToString() function returns a pointer to related error string.

### ERRORS

N/A

### ai\_GetLibraryVersion

## NAME

## ai\_GetLibraryVersion

Returns the version number of the shared library.

## **SYNOPSIS**

#include <itp\_driver.h>

int ai\_GetLibraryVersion (char\* version);

## DESCRIPTION

ai\_GetLibraryVersion() returns the version number of the ITP driver library through the version pointer to char.

### **RETURN VALUE**

On success, ai\_GetLibraryVersion() returns 0.

#### ERRORS

N/A

## SEE ALSO

N/A

ai\_mBasicRWRamTest

#### NAME

ai\_mBasicRWRamTest Execute a Basic R/W RAM Test diagnostic.

### **SYNOPSIS**

#include <itp driver.h>

```

int ai_mBasicRWRamTest (int mHandle, uint64_t StartAddress, uint64_t

EndAddress, char* ErrorString);

```

#### DESCRIPTION

ai\_mBasicRWRamTest() executes a test to diagnose the data and address buses between the CPU and a RAM area.

mHandle identifies the node to execute on.

StartAddress specifies the start address of the range and EndAddress specifies the end address of the range, within which, operations will be carried out to perform the diagnostic algorithm(s).

ai\_mBasicRWRamTest() assumes a 64-bit data bus width (for data bus, byte enable lane and data cell testing).

If an error is diagnosed, ErrorString will return the diagnostic information.

NOTES:

Prior to executing the function, the following actions may be carried out:

By default (if the PowerCheck option is not disabled via ai\_mConfig()), the function will first of all perform a power check on the target.

Also, by default (if the ScanChainSetup option is not disabled via ai\_mConfig()), the function will perform necessary actions to interrogate/bring up and ensure all target devices (cores) are alive on the scan chain.

Lastly, by default (if the SaveModifyArch option is not disabled via ai\_mConfig()), the function will perform necessary actions to force all connected devices (cores) in to debug mode (if not already in debug mode), and save the architectural state of the target core (again, if not already saved previously) to a 'processor state buffer'. The 'processor state buffer' is a storage area in host memory used to temporarily store the architectural state registers of the core, such that these registers can then be used for other debug operations. The action to save the 'processor state buffer' is a one-time only action, which only requires execution/re- execution if the target is reset, the core 'processor state buffer' was previously restored, or a new instance of the driver (.so) is loaded.

ai\_mBasicRWRamTest() is divided in to 5 sub-tests, executed in sequence.

- 1. Data bus hi/lo test.

- 2. Data bus shorts test.

- 3. Byte enables test.

- 4. Data test (writes/verifies patterns to every individual cell in the range specified).

- 5. Address bus test.

If any sub-test fails the diagnostic returns immediately, skipping execution of any subsequent sub-tests.

The 'Data test' sub-test uses machine code routines that operate in 32-bit mode only. Therefore, this diagnostic can only operate on the bottom 4G memory space (i.e. 0x0-0xFFFFFFFF).

#### **RETURN VALUE**

On successful completion of the diagnostic with no errors, ai\_mBasicRWRamTest() returns 0. On error, it will return one of the following values:

#### ERRORS

| AI_INVALID_PARAM              | Invalid parameter                                     |

|-------------------------------|-------------------------------------------------------|

| AI_VCC_NOT_FOUND              | Target not powered up                                 |

| AI_MAX_UNCORES_EXCEEDED       | Scan chain init: maximum possible Uncores exceeded    |

| AI_INVALID_CORE_IDCODE_DET    | Scan chain init: an invalid core IDCODE was detected  |

| AI_INVALID_UNCORE_IDCODE_DET  | Scan chain init: an invalid Uncore IDCOD was detected |

| AI_ERR_TAP_OWNERSHIP          | Scan chain init: error getting ownership of the TAP   |

| AI_CFG_JTAG                   | Scan chain init: Error configuring JTAG               |

| AI_SA_GREATER_THAN_EA         | Start address cannot be greater than end address      |

| AI_BASIC_RW_RAM_DATA_HILO     | Data bus hi/lo failure diagnosed                      |

| AI_BASIC_RW_RAM_DATA_SHORT    | Data bus shorts failure diagnosed                     |

| AI_BASIC_RW_RAM_BYTE_ENABLES  | Byte enables lane(s) failure diagnosed                |

| AI_BASIC_RW_RAM_DATA_TEST     | Data cell test failure diagnosed                      |

| AI_BASIC_RW_RAM_ADDRESS       | Address bus failure diagnosed                         |

| AI_RAM_TEST_HALTED_USR        | Execution of RAM test interrupted by user             |

| AI_RAM_TEST_HALTED_UNKNWN_SRC | Execution of RAM test interrupted by unknown source   |

| AI_ERR_PCT_INT_IOCTL        | Error reported from <code>IOCTL()</code> function      |

|-----------------------------|--------------------------------------------------------|

| AI_FILE_LOAD_ERR            | Error loading hex file (required for data cell test)   |

| AI_DBG_MODE_RAM_TEST        | Error during execution of RAM Test                     |

| AI_RESTORE_JTAG_CFG_DEFAULT | Error restoring JTAG/Configuration settings to default |

## SEE ALSO

- ai\_mRamBusTest

- ai\_mRamBusTestChannel

- ai\_mRamBusTestviaFIFO

- ai\_mRWRamTest

- ai\_mDRamRefreshTest

ai\_mBootRomBusTest

### NAME

# ai\_mBootRomBusTest

Execute a Boot ROM Bus Test diagnostic.

## SYNOPSIS

#include <itp\_driver.h>

```

int ai_mBootRomBusTest (int mHandle, uint64_t StartAddress, uint64_t

EndAddress, char* ErrorString);

```

## DESCRIPTION

ai\_mBootRomBusTest() executes a test to diagnose the data and address buses between the CPU and the boot ROM area. Because of the nature of ROM memory (i.e. read only), only read memory operations can be used to diagnose the buses.

mHandle identifies the node for the operation to be carried out on.

StartAddress specifies the start address of the range and EndAddress specifies the end address of the range, within which, operations will be carried out to perform the diagnostic algorithm(s).

NOTES:

Prior to executing the function, the following actions may be carried out:

By default (if the <code>PowerCheck</code> option is not disabled via <code>ai\_mConfig()</code>), <code>ai\_mBasicRWRamTest()</code> will first of all perform a power check on the target.

Also, by default (if the ScanChainSetup option is not disabled via ai\_mConfig()), the function will perform necessary actions to interrogate/bring up and ensure all target devices (cores) are alive on the scan chain.

Lastly, by default (if the SaveModifyArch option is not disabled via ai\_mConfig()), the function will perform necessary actions to force all connected devices (cores) in to debug mode (if not already in debug mode), and save the architectural state of the target core (again, if not already saved previously) to a 'processor state buffer'. The 'processor state buffer' is a storage area in host memory used to temporarily store the architectural state registers of the core, such that these registers can then be used for other debug operations. The action to save the 'processor state buffer' is a one-time only action, which only requires execution/re- execution if the target is reset, the core 'processor state buffer' was previously restored, or a new instance of the driver (.so) is loaded.

$\texttt{ai\_mBootRomBusTest}$  () is divided in to 2 sub-tests, executed in sequence.

- 1. Data bus test.

- 2. Address Bus Test.

If any sub-test fails, the diagnostic returns immediately, skipping execution of any subsequent sub-tests.

The test does not necessarily have to be execute on a ROM area of memory. It can be executed on a RAM area. However, the target range must have random data within it (the diagnostic algorithms assume random data in the range).

#### **RETURN VALUE**

On successful completion of the diagnostic with no errors, ai\_mBootRomBusTest() returns 0. On error, it will return one of the following values:

#### ERRORS

| AI_VCC_NOT_FOUND             | Target not powered up                                  |

|------------------------------|--------------------------------------------------------|

| AI_MAX_UNCORES_EXCEEDED      | Scan chain init: maximum possible Uncores exceeded     |

| AI_INVALID_CORE_IDCODE_DET   | Scan chain init: an invalid Core IDCODE was detected   |

| AI_INVALID_UNCORE_IDCODE_DET | Scan chain init: an invalid Uncore IDCODE was detected |

| AI_ERR_TAP_OWNERSHIP         | Scan chain init: error getting ownership of the TAP    |

| AI_CFG_JTAG                  | Scan chain init: error configuring JTAG                |

| AI_SA_GREATER_THAN_EA        | Start address cannot be greater than end address       |

| AI_ROM_BUS_FAIL              | Bus test diagnosed a failure                           |

| AI_ROM_TEST_HALTED_USR       | Execution of Boot ROM bus test interrupted by user     |

| AI_DBG_MODE_ROM_BUS          | Error during execution of Boot ROM bus test            |

| AI_RESTORE_JTAG_CFG_DEFAULT  | Error restoring JTAG/configuration settings to default |

## SEE ALSO

N/A

#### ai\_mCheckMemory

#### NAME

## ai mCheckMemory

Check that a memory block/range contains a specific value

#### **SYNOPSIS**

#include <itp driver.h>

int ai\_mCheckMemory (int mHandle, uint64\_t StartAddress, uint64\_t EndAddress, void\* FillValue, void\* CheckValue, ai\_Buswidth BusWidth, uint64\_t\* ErrorAddress, void\* ErrorData);

#### DESCRIPTION

ai\_mCheckMemory() submits instruction(s) to the target core on the node specified by mHandle, to execute the 'check memory' machine code routine on the target core, to check a memory block starting at StartAddress and ending at EndAddress for the value CheckValue. As each location is checked, it will be overwritten with the value FillValue.

BusWidth takes on one of the following values to specify the operand size for the operation.

- 8 8-bit operand size

- 16 16-bit operand size.

- 32 32-bit operand size

ErrorAddress will return the memory location in error on a failure occurrence, and ErrorData will return the data at the failing memory location.

During execution of the 'check memory' machine code routine, the target core will exit debug mode. The function will not return until the core has re-entered debug mode. Upon completion, the target core should immediately re-enter debug mode, at which point, the target core can then service ITP driver functions normally again.

Should the user wish to force re-entry to debug mode during execution of the 'check memory' machine code routine, he/she can do so by calling ai\_mStopTest() via a forked child process. ai\_mStopTest() will force debug mode re-entry, which will cause ai\_CheckMemory() to subsequently return.

No other ITP Driver functions (other than ai\_mStopTest()) should be called while ai\_mCheckMemory() is running. Because the target core is not in debug mode during user diagnostic execution, execution of other ITP Driver functions can force the target core to re-enter debug mode. In this case, ai\_mCheckMemory() behavior is undefined.

The 'check memory' machine code routine forms part of a collection of machine code routines which the ITP driver can execute. Since the routines are machine code, they must be downloaded and run from an area of memory accessible by the target core. UUTDiagsHexFile from ai\_mConfig() provides the ITP driver library with a pointer to the machine code file, and UUTDiagsBaseAddress, also from ai\_mConfig(), defines the memory base address from which the machine code will be run. Prior to calling the 'check memory' machine code routine, the function will check if the machine code routines exists at UUTDiagsBaseAddress, and if not, will proceed to download the file pointed to by UUTDiagsHexFile.

#### NOTES:

Prior to executing the function, the following actions may be carried out:

By default (if the <code>PowerCheck</code> option is not disabled via <code>ai\_mConfig()</code>), the function will first of all perform a power check on the target.

Also, by default (if the ScanChainSetup option is not disabled via ai\_mConfig()), the function will perform necessary actions to interrogate/bring up and ensure all target devices (cores) are alive on the scan chain.

Lastly, by default (if the SaveModifyArch option is not disabled via ai\_mConfig()), the function will perform necessary actions to force all connected devices (cores) in to debug mode (if not already in debug mode), and save the architectural state of the target core (again, if not already saved previously) to a 'processor state buffer'. The 'processor state buffer' is a storage area in host memory used to temporarily store the architectural state registers of the core, such that these registers can then be used for other debug operations. The action to save the 'processor state buffer' is a one-time only action, which only requires execution/re- execution if the target is reset, the core 'processor state buffer' was previously restored, or a new instance of the driver (.so) is loaded.

The machine code routines operate in 32-bit mode only, therefore any machine code routines will only operate in the bottom 4G memory space (i.e 0x0-0xFFFFFFF). Behavior is undefined if the range specified extends outside this area.

When calling ai\_mCheckMemory(), the user should ensure that memory range specified does not overlap into the UUTDiagsBaseAddress memory area reserved for execution of the machine code routines. Also, the user should ensure that memory has been initialized sufficiently to allow the machine code routines to run properly. In both cases, the function may fail to return normally (i.e. unless forced using ai StopTest()).

#### **RETURN VALUE**

On success, ai\_mCheckMemory() returns 0. On error, it will return one of the following values:

#### ERRORS

| AI_INVALID_PARAM              | Invalid parameter                                                 |

|-------------------------------|-------------------------------------------------------------------|

| AI_VCC_NOT_FOUND              | Target not powered up                                             |

| AI_MAX_UNCORES_EXCEEDED       | Scan chain init: maximum possible Uncores exceeded                |

| AI_INVALID_CORE_IDCODE_DET    | Scan chain init: an invalid core IDCODE was detected              |

| AI_INVALID_UNCORE_IDCODE_DET  | Scan chain init: an invalid Uncore IDCODE was detected            |

| AI_ERR_TAP_OWNERSHIP          | Scan chain init: rrror getting ownership of the TAP               |

| AI_CFG_JTAG                   | Scan chain init: error configuring JTAG                           |

| AI_DBG_MODE_CHECK_MEM         | Error during execution of check memory operation                  |

| AI_CHECK_MEM_FAIL             | Memory failure                                                    |

| AI_CHECK_MEM_HALTED_USR       | Execution of check memory operation interrupted by user           |

| AI_CHECK_MEM_HALTED_UNKNWN_SR | C Execution of check operation interrupted by unknown source      |

| AI_SA_GREATER_THAN_EA         | Start address cannot be greater than end address                  |

| AI_NO_EXEC_HALT_STATE         | Target is halted. Unable to execute user diagnostic               |

| AI_NO_EXEC_WAIT_FOR_SIPI_STAT | ETarget indicates 'WAIT FOR SIPI' state. Unable to run diagnostic |

| AI_NO_EXEC_SHUTDOWN_STATE     | Target in 'SHUTDOWN' state. Unable to run diagnostic              |

| AI_ERR_PCT_INT_IOCTL          | Error reported from IOCTL() function                              |

| AI_RESTORE_JTAG_CFG_DEFAULT   | Error restoring JTAG configuration settings to default            |

## FILES

Pentcode.hex - machine code routines collection. Can be installed to any directory.

UUTDiagsHexFile from ai\_mConfig() provides the ITP driver library with a pointer to the

machine code file.

#### SEE ALSO

ai\_mFillMemory

ai\_mStopTest

### NAME

ai\_mClose

## ai\_mClose

Close communication channel with ITP Driver JTAG Controller device.

## **SYNOPSIS**

```

#include <itp_driver.h>

void ai_mClose (int mHandle);

```

## DESCRIPTION

ai\_mClose() closes the ITP Driver 'connection' specified by mHandle.

The function submits a reset to the ITP driver JTAG controller device, thereby relinquishing control over the XDP and JTAG lines. It then proceeds to unmap the ITP Driver JTAG controller from memory space, and finally closes the file handle to the device.

## **RETURN VALUE**

N/A

#### ERRORS

N/A

#### SEE ALSO

ai mOpen

ai\_mOpenEx

#### NAME

## ai\_mConfig

Set up configuration parameters.

## SYNOPSIS

#include <itp\_driver.h>

```

int ai_mConfig (int mHandle, uint16_t ResetPulseDuration, FILE

*UUTDiagsHexFile, uint64_t UUTDiagsBaseAddress, bool PowerCheck, bool

ScanChainSetup, bool SaveModifyArch);

```

## DESCRIPTION

ai\_mConfig() sets up various configuration parameters for the node identified by mHandle that may be required by other ITP driver library function calls.

ResetPulseDuration specifies the length of pulse (in mSecs) to be applied to the DBR line (XDP interface - HOOK7) when the ai\_mResetUUT() or ai\_mRunUUT() functions are invoked.

UUTDiagsHexFile provides a file pointer to the UUT diagnostics hex file. The UUT diagnostics hex file contains the machine code language routines that are used by the ITP driver library to carry out ROM CRC checks, fill memory commands, and check memory commands. Some RAM test diagnostics also have fill and check memory commands built into their algorithms.

UUTDiagsBaseAddress provides the base address in memory where the UUT diagnostics hex file will be downloaded and executed from. Diagnostics can only be downloaded and/or executed from the bottom 4GB of memory (0x0 - 0xfffffff).

PowerCheck provides a global parameter to the other ITP driver library functions informing them to execute a power check first, before continuing to execute their designated function. Default value is true (i.e. do a power check)

ScanChainSetup provides a global parameter to the other ITP driver library functions informing them to check and perform (if necessary) the required scan chain interrogation and setup before executing their designated function. Default value is true (i.e. check and perform scan-chain interrogation/set-up).

SaveModifyArch provides a global parameter to the other ITP driver library functions informing them to check and perform (if necessary) the debug mode entry and processor state save routines before executing their designated function. Most of the ITP driver functions require the target CPU to be in debug mode, and the state of the processor at the debug mode entry point to be saved to a buffer within the ITP driver. Default value is true (i.e. check and perform debug mode entry and save processor state routines).

ai\_mConfig

## **RETURN VALUE**

On success,  $\texttt{ai\_mConfig}()$  returns 0. On error, it will return one of the following values:

## ERRORS

AI\_INVALID\_PARAM Invalid parameter.

#### **SEE ALSO**

N/A

NAME

## ai mCPUID

Submit a CPUID instruction and retrieve CPUID info from target core.

#### **SYNOPSIS**

#include <itp driver.h>

```

int ai_mCPUID (int mHandle, uint32_t inEAX, uint32_t inECX, uint32_t

*retEAX, uint32_t *retEBX, uint32_t *retECX, uint32_t *retEDX);

```

#### DESCRIPTION

ai\_mCPUID() submits a CPUID instruction to the target core, on the node specified by mHandle, with the data presented in inEAX and inECX as the inputs. The output from the execution of the CPUID instruction is saved and returned in retEAX, retEBX, retECX and retEDX. See Intel 64 and IA-32 Architectures Software Developer Manual Volume 2A for more information on the CPUID function.

On some processors CPUID functionality is not available. Prior to submitting the CPUID instruction for execution, the function performs an operation to check if such functionality is available.

The input and output parameters do not have any effect on the 'processor state buffer' held in host memory. (i.e. the target core 'processor stat buffer' remains unaffected through the execution of this function).

NOTES:

Prior to executing the function, the following actions may be carried out:

By default (if the <code>PowerCheck</code> option is not disabled via <code>ai\_mConfig()</code>), the function will first of all perform a power check on the target.

Also, by default (if the ScanChainSetup option is not disabled via ai\_mConfig()), the function will perform necessary actions to interrogate/bring up and ensure all target devices (cores) are alive on the scan chain.

Lastly, by default (if the SaveModifyArch option is not disabled via ai\_mConfig()), the function will perform necessary actions to force all connected devices (cores) in to debug mode (if not already in debug mode), and save the architectural state of the target core (again, if not already saved previously) to a 'processor state buffer'. The 'processor state buffer' is a storage area in host memory used to temporarily store the architectural state registers of the core, such that these registers can then be used for other debug operations. The action to save the 'processor state buffer' is a one-time only action, which only requires execution/re-execution if the target is reset, the core 'processor state buffer' was previously restored, or a new instance of the driver (.so) is loaded.

## **RETURN VALUE**

On success, ai\_mCPUID() returns 0. On error, it will return one of the following values:

## ERRORS

| AI_VCC_NOT_FOUND             | Target not powered up                                  |

|------------------------------|--------------------------------------------------------|

| AI_MAX_UNCORES_EXCEEDED      | Scan chain init: maximum possible UNCORES exceeded     |

| AI_INVALID_CORE_IDCODE_DET   | Scan chain init: an invalid core IDCODE was detected   |

| AI_INVALID_UNCORE_IDCODE_DET | Scan chain init: an invalid Uncore IDCODE was detected |

| AI_ERR_TAP_OWNERSHIP         | Scan chain init: error getting ownership of the TAP    |

| AI_CFG_JTAG                  | Scan chain init: error configuring JTAG                |

| AI_CPUID_NOT_AVAIL           | Target core reports CPUID functionality not available  |

| AI_DBG_MODE_CPUID            | Error during execution of CPUID operation              |

| AI_RESTORE_JTAG_CFG_DEFAULT  | Error restoring JTAG configuration settings to default |

## SEE ALSO

N/A

#### ai\_mDownloadUserDiag

#### NAME

## ai mDownloadUserDiag

Download a user diagnostic to target memory.

#### **SYNOPSIS**

#include <itp driver.h>

int ai\_mDownloadUserDiag (int mHandle, FILE \*userdiagfilefd, uint64\_t

BaseAddress);

#### DESCRIPTION

ai\_mDownloadUserDiag() submits instruction(s) to the target core, on the node specified by mHandle, to download the data from the binary file pointed to by userdiagfilefd, to a memory area with the base address location specified by BaseAddress.

The file pointed to by userdiagfilefd must be of Intel HEX format. Normally, the code for such Intel HEX format is written in assembly language and compiled using a macro assembler of some description, such as the Microsoft Macro Assembler (MASM).

NOTES:

Prior to executing the function, the following actions may be carried out:

By default (if the <code>PowerCheck</code> option is not disabled via <code>ai\_mConfig()</code>), the function will first of all perform a power check on the target.

Also, by default (if the ScanChainSetup option is not disabled via ai\_mConfig()), the function will perform necessary actions to interrogate/bring up and ensure all target devices (cores) are alive on the scan chain.

Lastly, by default (if the SaveModifyArch option is not disabled via ai\_mConfig()), the function will perform necessary actions to force all connected devices (cores) in to debug mode (if not already in debug mode), and save the architectural state of the target core (again, if not already saved previously) to a 'processor state buffer'. The 'processor state buffer' is a storage area in host memory used to temporarily store the architectural state registers of the core, such that these registers can then be used for other debug operations. The action to save the 'processor state buffer' is a one-time only action, which only requires execution/re- execution if the target is reset, the core 'processor state buffer' was previously restored, or a new instance of the driver (.so) is loaded.

On debug mode entry (and after saving the architectural state), the target core will be in placed in 32-bit operating mode. As shown in the example below, user diagnostics should assume 32-bit mode operation. Based upon the 32-bit operation assumption, it is not possible for user diagnostics to execute above the 4GB boundary (0xfffffff). Any attempt to download user diagnostics using BaseAddress greater than 0xffffffff will be rejected. Users should ensure their user diagnostic(s) do not extend

ai\_mDownloadUserDiag

beyond the 4GB boundary. In this case, no error is produced, but execution of the user diagnostic will produce undefined behavior.

#### **RETURN VALUE**

On success, ai\_mDownloadUserDiag() returns 0. On error, it will return one of the following values:

#### ERRORS

| AI_VCC_NOT_FOUND             | Target not powered up                                               |

|------------------------------|---------------------------------------------------------------------|

| AI_MAX_UNCORES_EXCEEDED      | Scan chain init: maximum possible Uncores exceeded                  |

| AI_INVALID_CORE_IDCODE_DET   | Scan chain init: an invalid Core IDCODE was detected                |

| AI_INVALID_UNCORE_IDCODE_DET | Scan chain init: an invalid Uncore IDCODE was detected              |

| AI_ERR_TAP_OWNERSHIP         | Scan chain init: error getting ownership of the TAP                 |

| AI_CFG_JTAG                  | Scan chain init: error configuring JTAG                             |

| AI_DBG_MODE_DWNLD_USR_DIAG   | Error during execution of user diagnostic                           |

| AI_RESTORE_JTAG_CFG_DEFAULT  | <sup>1</sup> Error restoring JTAG configuration settings to default |

#### EXAMPLE

The code below demonstrates the format of a user diagnostic, and how it is written using assembly language such that it can be properly invoked by the ai\_mExecuteUserDiag() call, and return the target core in a halted state (debug mode) on completion of the routine.

.386P CODE SEGMENT USE32 ASSUME CS:CODE,DS:CODE BreakPoint: JMP Breakpoint ;\* First line (obligatory!) MOV ECX,0000B8000H ;\* code MOV EAX,0ABCDEF10H ;\* code MOV [ECX],EAX ;\* code JMP BreakPoint ;\* Last line (obligatory!) ;\*\*\*\*\*

;CODE ENDS HERE.

END

Note that the first and last lines are marked as obligatory. These lines must be present in the diagnostic otherwise it may not run or return to debug mode after completion. The user should insert the diagnostic routine between these two lines.

Although this example illustrates moving values into GPRs, data can be passed into and returned from the diagnostic by calling the ai\_mReadGPR() and ai\_mWriteGPR() prior to or after execution of the diagnostic.

#### **SEE ALSO**

ai\_mExecuteUserDiag

#### ai\_mDRamRefreshTest

#### NAME

## ai mDRamRefreshTest

Execute a DRAM Refresh Test diagnostic.

#### **SYNOPSIS**

#include <itp driver.h>

```

int ai_mDRamRefreshTest (int mHandle, uint64_t StartAddress, uint64_t

EndAddress, double RefreshDelay, char* ErrorString);

```

#### DESCRIPTION

ai\_mDRamRefreshTest() executes a test to find and diagnose refresh problems on a DRAM area.

mHandle identifies the node to execute on.

StartAddress specifies the start address of the range and EndAddress specifies the end address of the range, within which, operations will be carried out to perform the diagnostic algorithm(s).

RefreshDelay specifies the delay (in secs) between filling and checking the memory range, in each pass of the diagnostic.

If an error is diagnosed, ErrorString will return the diagnostic information.

NOTES:

Prior to executing the function, the following actions may be carried out:

By default (if the <code>PowerCheck</code> option is not disabled via <code>ai\_mConfig()</code>), the function will first of all perform a power check on the target.

Also, by default (if the ScanChainSetup option is not disabled via ai\_mConfig()), the function will perform necessary actions to interrogate/bring up and ensure all target devices (cores) are alive on the scan chain.

Lastly, by default (if the SaveModifyArch option is not disabled via ai\_mConfig()), the function will perform necessary actions to force all connected devices (cores) in to debug mode (if not already in debug mode), and save the architectural state of the target core (again, if not already saved previously) to a 'processor state buffer'. The 'processor state buffer' is a storage area in host memory used to temporarily store the architectural state registers of the core, such that these registers can then be used for other debug operations. The action to save the 'processor state buffer' is a one-time only action, which only requires execution/re- execution if the target is reset, the core 'processor state buffer' was previously restored, or a new instance of the driver (.so) is loaded.

The ai\_mDRamRefreshTest() function uses machine code routines that operate in 32-bit mode only. Therefore, this diagnostic can only operate on the bottom 4G memory space (i.e. 0x0-0xFFFFFFF).

This is a 2-pass test. The first pass writes/verifies zeroes (0's) to each cell location, while the 2nd pass writes/verifies ones (1's) to each cell location.

#### **RETURN VALUE**

On successful completion of the diagnostic with no errors, ai\_mDRamRefreshTest() returns 0. On error, it will return one of the following values:

#### ERRORS

| AI_VCC_NOT_FOUND              | Target not powered up                                  |

|-------------------------------|--------------------------------------------------------|

| AI_MAX_UNCORES_EXCEEDED       | Scan chain init: maximum possible Uncores exceeded     |

| AI_INVALID_CORE_IDCODE_DET    | Scan chain init: an invalid Core IDCODE was detected   |

| AI_INVALID_UNCORE_IDCODE_DET  | Scan chain init: an invalid Uncore IDCODE was detected |

| AI_ERR_TAP_OWNERSHIP          | Scan chain init: error getting ownership of the TAP    |

| AI_CFG_JTAG                   | Scan chain init: error configuring JTAG                |

| AI_SA_GREATER_THAN_EA         | Start address cannot be greater than end address       |

| AI_DRAM_REFRESH               | DRAM refresh failure diagnosed                         |

| AI_RAM_TEST_HALTED_USR        | Execution of RAM Test interrupted by user              |

| AI_RAM_TEST_HALTED_UNKNWN_SRC | RAM test interrupted by unknown source                 |

| AI_ERR_PCT_INT_IOCTL          | Error reported from $IOCTL$ ( ) function               |

| AI_FILE_LOAD_ERR              | Error loading hex file (required for test)             |

| AI_ERR_PCT_INT_IOCTL          | Error reported from $IOCTL$ ( ) function               |

| AI_DBG_MODE_RAM_TEST          | Error during execution of RAM test                     |

| AI_RESTORE_JTAG_CFG_DEFAULT   | Error restoring JTAG configuration settings to default |

#### SEE ALSO

- ai\_mRamBusTest

- ai mRamBusTestChannel

- ai\_mRamBusTestviaFIFO

- ai mBasicRWRamTest

## ai\_mDRamRefreshTest

## ai mRWRamTest

#### ai\_mEnableoxmdebug

#### NAME

ai\_mEnableoxmdebug Enable target ureg\_raw capability

#### **SYNOPSIS**

```

#include <itp_ureg_raw.h>

int ai_mEnableoxmdebug (int mHandle);

```

#### DESCRIPTION

ai\_mEnableoxmdebug() enables the target CPU, for the node identified by mHandle, to be receptive to uregraw type scans. The target is briefly put in to debug mode to carry out the operation, after which debug mode is exited, and the target is left in a running state again. This function is provided mainly as an interface for Intel CScripts. THIS API IS ONLY APPLICABLE TO INTEL IVY BRIDGE TARGETS.

#### NOTES:

Prior to executing the function, the following actions may be carried out:

By default (if the PowerCheck option is not disabled via ai\_mConfig()), the function will first of all perform a power check on the target.

Also, by default (if the ScanChainSetup option is not disabled via ai\_mConfig()), the function will perform necessary actions to interrogate/bring up and ensure all target devices (cores) are alive on the scan chain.

The scan chain will be returned to its original state on function completion.

#### **RETURN VALUE**

On success, ai mEnableoxmdebug() returns 0. On error, it will return one of the following values:

#### ERRORS

| AI_VCC_NOT_FOUND             | Target not powered up                                  |

|------------------------------|--------------------------------------------------------|

| AI_MAX_UNCORES_EXCEEDED      | Scan chain init: maximum possible Uncores exceeded     |

| AI_INVALID_CORE_IDCODE_DET   | Scan chain init: an invalid Core IDCODE was detected   |

| AI_INVALID_UNCORE_IDCODE_DET | Scan chain init: an invalid Uncore IDCODE was detected |

| AI_ERR_TAP_OWNERSHIP         | Scan chain init: error getting ownership of the TAP    |

|                              |                                                        |

# ai\_mEnableoxmdebug

| AI_CFG_JTAG                  | Scan chain init: error configuring JTAG                |

|------------------------------|--------------------------------------------------------|

| AI_UREG_RAW_NOT_IMPLEMENTED  | Not a valid function (possibly not IvyBridge target)   |

| AI_DBG_MODE_ENABLE_OXM_DEBUG | Error during execution of Enableoxmdebug operation     |

| AI_RESTORE_JTAG_CFG_DEFAULT  | Error restoring JTAG configuration settings to default |

# SEE ALSO

- ai\_muregraw

- ai\_muregraw64

#### ai\_mEnableRAMAreaasCAR

#### NAME

# ai\_mEnableRAMAreaasCAR

Set up a RAM area as cacheable.

## **SYNOPSIS**

#include <itp driver.h>

```

int ai_mEnableRAMAreaasCAR (int mHandle, uint64_t CarBaseAddress,

uint64_t CarSize);

```

## DESCRIPTION

ai\_mEnableRAMAreaasCAR() submits instruction(s) to the target core, on the node specified by mHandle, to invalidate its cache, and set up an area of target memory as cacheable. CarSize defines the size of the area to be defined as cacheable, and CarBaseAddress defines the base address of the area to be made cacheable.

## NOTES:

Prior to executing the function, the following actions may be carried out:

By default (if the <code>PowerCheck</code> option is not disabled via <code>ai\_mConfig()</code>), the function will first of all perform a power check on the target.

Also, by default (if the ScanChainSetup option is not disabled via ai\_mConfig()), the function will perform necessary actions to interrogate/bring up and ensure all target devices (cores) are alive on the scan chain.

Lastly, by default (if the SaveModifyArch option is not disabled via ai\_mConfig()), the function will perform necessary actions to force all connected devices (cores) in to debug mode (if not already in debug mode), and save the architectural state of the target core (again, if not already saved previously) to a 'processor state buffer'. The 'processor state buffer' is a storage area in host memory used to temporarily store the architectural state registers of the core, such that these registers can then be used for other debug operations. The action to save the 'processor state buffer' is a one-time only action, which only requires execution/re- execution if the target is reset, the core 'processor state buffer' was previously restored, or a new instance of the driver (.so) is loaded.

CAR can only be defined within the bottom 4GB memory region (i.e. 0x0 - 0xffffffff).

## **RETURN VALUE**

On success, ai\_mEnableRAMAreaasCAR() returns 0. On error, it will return one of the following values:

## ERRORS

| AI_VCC_NOT_FOUND             | Target not powered up                                  |

|------------------------------|--------------------------------------------------------|

| AI_MAX_UNCORES_EXCEEDED      | Scan chain init: maximum possible Uncores exceeded     |

| AI_INVALID_CORE_IDCODE_DET   | Scan chain init: an invalid Core IDCODE was detected   |

| AI_INVALID_UNCORE_IDCODE_DET | Scan chain init: an invalid Uncore IDCODE was detected |

| AI_ERR_TAP_OWNERSHIP         | Scan chain init: error getting ownership of the TAP    |

| AI_CFG_JTAG                  | Scan chain init: error configuring JTAG                |

| AI_DBG_MODE_SETUP_CAR_RAM    | Error during setup of RAM area                         |

| AI_RESTORE_JTAG_CFG_DEFAULT  | Error restoring JTAG configuration settings to default |

# SEE ALSO

N/A

#### ai\_mEnableUUTDiagsAreaasCAR

#### NAME

# ai mEnableUUTDiagsAreaasCAR

Set up area from where machine code routines are run from as cacheable.

#### **SYNOPSIS**

#include <itp\_driver.h>

int ai\_mEnableUUTDiagsAreaasCAR (int mHandle);

## DESCRIPTION

ai\_mEnableUUTDiagsAreaasCAR() submits instruction(s) to the target core, on the node specified by mHandle, to invalidate its cache, and set up a 4KB area around the machine code routines as cacheable. All memory accesses (other than to the cacheable machine code area) will then be directed to physical memory, as opposed to cache.

#### NOTES:

Prior to executing the function, the following actions may be carried out:

By default (if the PowerCheck option is not disabled via ai\_mConfig()), the function will first of all perform a power check on the target.

Also, by default (if the ScanChainSetup option is not disabled via ai\_mConfig()), the function will perform necessary actions to interrogate/bring up and ensure all target devices (cores) are alive on the scan chain.

Lastly, by default (if the SaveModifyArch option is not disabled via ai\_mConfig()), the function will perform necessary actions to force all connected devices (cores) in to debug mode (if not already in debug mode), and save the architectural state of the target core (again, if not already saved previously) to a 'processor state buffer'. The 'processor state buffer' is a storage area in host memory used to temporarily store the architectural state registers of the core, such that these registers can then be used for other debug operations. The action to save the 'processor state buffer' is a one-time only action, which only requires execution/re- execution if the target is reset, the core 'processor state buffer' was previously restored, or a new instance of the driver (.so) is loaded.

#### **RETURN VALUE**

On success, ai\_mEnableUUTDiagsAreaasCAR() returns 0. On error, it will return one of the following values

#### ERRORS

# ai\_mEnableUUTDiagsAreaasCAR

| AI_VCC_NOT_FOUND               | Target not powered up                                  |

|--------------------------------|--------------------------------------------------------|

| AI_MAX_UNCORES_EXCEEDED        | Scan chain init: maximum possible Uncores exceeded     |

| AI_INVALID_CORE_IDCODE_DET     | Scan chain init: an invalid Core IDCODE was detected   |

| AI_INVALID_UNCORE_IDCODE_DET   | Scan chain init: an invalid Uncore IDCODE was detected |

| AI_ERR_TAP_OWNERSHIP           | Scan chain init: error getting ownership of the TAP    |

| AI_CFG_JTAG                    | Scan chain init: error configuring JTAG                |

| AI_DBG_MODE_SETUP_CAR_PENTCODE | Error during setup of UUT diags area for CAR           |

| AI_RESTORE_JTAG_CFG_DEFAULT    | Error restoring JTAG configuration settings to default |

## SEE ALSO

ai\_mEnableRAMAreaasCAR

ai\_mEnterDebugMode

#### NAME

# ai mEnterDebugMode

Force all connected CPU core(s) into debug mode.

#### **SYNOPSIS**

#include <itp\_driver.h>

int ai mEnterDebugMode (int mHandle);

#### DESCRIPTION

ai\_mEnterDebugMode() forces all connected CPU cores on the node identified by mHandle into debug mode. This will halt all connected CPU core(s) at their current state. Debug mode is a temporary state, which the CPU core must be in to execute most of the ITP Driver library functions.

#### NOTES:

Prior to executing the function, the following actions may be carried out:

By default (if the PowerCheck option is not disabled via ai\_mConfig()), the function will first of all perform a power check on the target.

Also, by default (if the ScanChainSetup option is not disabled via ai\_mConfig()), the function will perform necessary actions to interrogate/bring up and ensure all target devices (cores) are alive on the scan chain.

#### **RETURN VALUE**

On success completion of the sequence, ai\_mEnterDebugMode() returns 0. On error, it will return one of the following values:

#### ERRORS

| AI_VCC_NOT_FOUND             | Target not powered up                                  |

|------------------------------|--------------------------------------------------------|

| AI_MAX_UNCORES_EXCEEDED      | Scan chain init: maximum possible Uncores exceeded     |

| AI_INVALID_CORE_IDCODE_DET   | Scan chain init: an invalid Core IDCODE was detected   |

| AI_INVALID_UNCORE_IDCODE_DET | Scan chain init: an invalid Uncore IDCODE was detected |

| AI_ERR_TAP_OWNERSHIP         | Scan chain init: error getting ownership of the TAP    |

| AI_CFG_JTAG                  | Scan chain init: error configuring JTAG                |

|                              |                                                        |

# ai\_mEnterDebugMode

| AI_DBG_MODE_ENTER           | Error during execution to put CPU cores into debug more |

|-----------------------------|---------------------------------------------------------|

| AI_RESTORE_JTAG_CFG_DEFAULT | Error restoring JTAG configuration settings to default  |

# SEE ALSO

ai\_mGetDebugModeStatus

ai\_mExecuteUserDiag

#### NAME

ai\_mExecuteUserDiag Execute a user diagnostic.

# SYNOPSIS

#include <itp\_driver.h>

int ai\_mExecuteUserDiag (int mHandle, uint64\_t BaseAddress);

## DESCRIPTION

ai\_mExecuteUserDiag() submits instruction(s) to the target core, on the node identified by mHandle, to execute the user diagnostic with the base address location specified by BaseAddress.

During execution of the user diagnostic, the target core will exit debug mode. The function will not return until the core has re-entered debug mode. Upon completion of the diagnostic, the target core should immediately re-enter debug mode, at which point, the target core can then service ITP driver functions normally again.

Should the user wish to force re-entry to debug mode during execution of the user diagnostic, he/she can do so by calling ai\_mStopTest() via a forked child process.ai\_mStopTest() will force debug mode re-entry, which will cause ai\_mExecuteUserDiag() to subsequently return.

No other ITP Driver functions (other than ai\_mStopTest()) should be called while ai\_mExecuteUserDiag() is running. Because the target core is not in debug mode during user diagnostic execution, execution of other ITP Driver functions could force the target core to re-enter debug mode. In this case, ai mExecuteUserDiag() behavior is undefined.

Data can be passed into and returned from the diagnostic by calling the <code>ai\_mReadGPR()</code> and <code>ai\_mWriteGPR()</code> prior to, or after execution, of the diagnostic.

NOTES:

Prior to executing the function, the following actions may be carried out:

By default (if the <code>PowerCheck</code> option is not disabled via <code>ai\_mConfig()</code>), the function will first of all perform a power check on the target.

Also, by default (if the ScanChainSetup option is not disabled via ai\_mConfig()), the function will perform necessary actions to interrogate/bring up and ensure all target devices (cores) are alive on the scan chain.

Lastly, by default (if the SaveModifyArch option is not disabled via ai\_mConfig()), the function will perform necessary actions to force all connected devices (cores) in to debug mode (if not already in debug mode), and save the architectural state of the target core (again, if not already saved previously)

to a 'processor state buffer'. The 'processor state buffer' is a storage area in host memory used to temporarily store the architectural state registers of the core, such that these registers can then be used for other debug operations. The action to save the 'processor state buffer' is a one-time only action, which only requires execution/re- execution if the target is reset, the core 'processor state buffer' was previously restored, or a new instance of the driver (.so) is loaded.

On debug mode entry (and after saving the architectural state), the target core will be in placed in 32-bit operating mode. User diagnostics should assume 32-bit mode operation. Based upon the 32-bit operation assumption, it is not possible for user diagnostics to execute above the 4GB boundary (0xffffffff). Any attempt to execute user diagnostics using BaseAddress greater than 0xffffffff will be rejected. Users should ensure their user diagnostic(s) do not extend beyond the 4GB boundary. In this case, no error is produced, but execution of the user diagnostic will produce undefined behavior.

#### **RETURN VALUE**

On success, ai mExecuteUserDiag() returns 0. On error, it will return one of the following values:

#### ERRORS

| AI_INVALID_PARAM               | Invalid parameter                                                      |

|--------------------------------|------------------------------------------------------------------------|

| AI_VCC_NOT_FOUND               | Target not powered up                                                  |

| AI_MAX_UNCORES_EXCEEDED        | Scan chain init: maximum possible Uncores exceeded                     |

| AI_INVALID_CORE_IDCODE_DET     | Scan chain init: an invalid Core IDCODE was detected                   |

| AI_INVALID_UNCORE_IDCODE_DET   | Scan chain init: an invalid Uncore IDCODE was detected                 |

| AI_ERR_TAP_OWNERSHIP           | Scan chain init: error getting ownership of the TAP                    |

| AI_CFG_JTAG                    | Scan chain init: error configuring JTAG                                |

| AI_DBG_MODE_EXEC_USR_DIAG      | Error during execution of user diagnostic                              |

| AI_EXEC_USR_DIAG_HALTED_USR    | Error of user diagnostic operation interrupted by user                 |

| AI_NO_EXEC_HALT_STATE          | Target core is in HALT state – cannot execute user diagnostic          |

| AI_NO_EXEC_WAIT_FOR_SIPI_STATE | Target core is in WAIT FOR SIPI state – cannot execute user diagnostic |

| AI_NO_EXEC_SHUTDOWN_STATE      | Target core is in SHUTDOWN state – cannot execute user diagnostic      |

| AI_ERR_PCT_INT_IOCTL           | Error reported from <code>IOCTL()</code> function                      |

| AI_RESTORE_JTAG_CFG_DEFAULT    | Error restoring JTAG configuration settings to default                 |

#### **SEE ALSO**

# ai\_mExecuteUserDiag

- ai\_mDownloadUserDiag

- ai\_mStopTest

ai\_mExitDebugMode

NAME

# ai mExitDebugMode

Force all connected CPU core(s) out of debug mode.

## **SYNOPSIS**

#include <itp\_driver.h>

int ai\_mExitDebugMode (int mHandle);

## DESCRIPTION

ai\_mExitDebugMode() forces all connected CPU cores on the node identified by mHandle out of debug mode, if they are in debug mode. This will restart all connected CPU core(s) from their current debug mode state. The function also primes the ITP Driver FPGA controller device PRDY interrupt mechanism, to allow any subsequent PRDY pulses (indicative of debug mode activity, such as breakpoints) to be detected.

Before attempting the exit debug mode operation, each individual core's "processor state buffer" will be restored (if it has been saved/extracted from the core).

Also, before attempting the exit debug mode operation, the ITP Driver controller device is primed to halt the CPU core(s) on detection of any subsequent activity on the CPU RESET signal (i.e. a ' debug mode at reset condition'). However, execution of ai\_mclose() will negate the ability to halt the CPU core(s) on the occurrence of a CPU RESET.

Debug mode status is not checked on completion of the exit debug mode operation. (i.e. the function does not check that all connected CPU core(s) have exited debug mode).

NOTES:

Prior to executing the function, the following actions may be carried out:

By default (if the <code>PowerCheck</code> option is not disabled via <code>ai\_mConfig()</code>), the function will first of all perform a power check on the target.

Also, by default (if the ScanChainSetup option is not disabled via ai\_mConfig()), the function will perform necessary actions to interrogate/bring up and ensure all target devices (cores) are alive on the scan chain.

## **RETURN VALUE**

On success completion of the sequence, ai\_mExitDebugMode() returns 0. On error, it will return one of the following values:

## ERRORS

| AI_VCC_NOT_FOUND             | Target not powered up                                  |

|------------------------------|--------------------------------------------------------|

| AI_MAX_UNCORES_EXCEEDED      | Scan chain init: maximum possible Uncores exceeded     |

| AI_INVALID_CORE_IDCODE_DET   | Scan chain init: an invalid Core IDCODE was detected   |

| AI_INVALID_UNCORE_IDCODE_DET | Scan chain init: an invalid Uncore IDCODE was detected |

| AI_ERR_TAP_OWNERSHIP         | Scan chain init: error getting ownership of the TAP    |

| AI_CFG_JTAG                  | Scan chain init: error configuring JTAG                |

| AI_DBG_MODE_STS              | Error during execution of get debug mode status        |

| AI_DBG_MODE_PROC_REGS        | Error during execution of restoring CPU core registers |

| AI_DBG_MODE_WAKEUP_PREQ      | Error during execution of WAKEUP_PREQ operation        |

| AI_ERR_PCT_INT_IOCTL         | Error from IOCTL() function                            |

| AI_DBG_MODE_EXIT             | Error during exit debug mode operation                 |

| AI_RESTORE_JTAG_CFG_DEFAULT  | Error restoring JTAG configuration settings to default |

# SEE ALSO

| ai_mEnterDebugMode     |

|------------------------|

| ai_mGetDebugModeStatus |

| ai_mWaitForDebugMode   |

#### ai\_mFillMemory

#### NAME

## ai mFillMemory

Fill a memory block/range with a specific value.

## **SYNOPSIS**

#include <itp driver.h>

```

int ai_mFillMemory (int mHandle, uint64_t StartAddress, uint64_t

EndAddress, void* FillValue, AI_buswidth BusWidth);

```

## DESCRIPTION

ai\_mFillMemory() submits instruction(s) to the target core on the node specified by mHandle, to execute the 'fill memory' machine code routine on the target core, to fill a memory block starting at StartAddress and ending at EndAddress with the value FillValue.

BusWidth takes on one of the following values to specify the operand size for the operation:

- 8 8-bit operand size

- 16 16-bit operand size.

- 32 32-bit operand size.

During execution of the 'fill memory' machine code routine, the target core will exit debug mode. The function will not return until the core has re-entered debug mode. Upon completion, the target core should immediately re-enter debug mode, at which point, the target core can then service ITP driver functions normally again.

Should the user wish to force re-entry to debug mode during execution of the 'fill memory' machine code routine, he/she can do so by calling ai\_mStopTest() via a forked child process. ai\_mStopTest() will force debug mode re-entry, which will cause ai\_mFillMemory() to subsequently return.

No other ITP Driver functions (other than ai\_mStopTest()) should be called while ai\_mFillMemory() is running. Because the target core is not in debug mode during user diagnostic execution, execution of other ITP Driver functions can force the target core to re-enter debug mode. In this case, ai\_mFillMemory() behavior is undefined.

The 'fill memory' machine code routine forms part of a collection of machine code routines which the ITP driver can execute. Since the routines are machine code, they must be downloaded and run from an area of memory accessible by the target core. UUTDiagsHexFile from ai\_mConfig() provides the ITP driver library with a pointer to the machine code file, and UUTDiagsBaseAddress, also from ai\_mConfig(), defines the memory base address from which the machine code will be run. Prior to calling the 'fill memory' machine code routine, the function will check if the machine code routines exist

## ai\_mFillMemory

at UUTDiagsBaseAddress, and if not, will proceed to download the file pointed to by UUTDiagsHexFile.

## NOTES:

Prior to executing the function, the following actions may be carried out:

By default (if the <code>PowerCheck</code> option is not disabled via <code>ai\_mConfig()</code>), the function will first of all perform a power check on the target.

Also, by default (if the ScanChainSetup option is not disabled via ai\_mConfig()), the function will perform necessary actions to interrogate/bring up and ensure all target devices (cores) are alive on the scan chain.

Lastly, by default (if the SaveModifyArch option is not disabled via ai\_mConfig()), the function will perform necessary actions to force all connected devices (cores) in to debug mode (if not already in debug mode), and save the architectural state of the target core (again, if not already saved previously) to a 'processor state buffer'. The 'processor state buffer' is a storage area in host memory used to temporarily store the architectural state registers of the core, such that these registers can then be used for other debug operations. The action to save the 'processor state buffer' is a one-time only action, which only requires execution/re- execution if the target is reset, the core 'processor state buffer' was previously restored, or a new instance of the driver (.so) is loaded.

The machine code routines operate in 32-bit mode only, therefore any machine code routines will only operate in the bottom 4G memory space (i.e 0x0-0xFFFFFFF). Behavior is undefined if the range specified extends outside this area.

When calling ai\_mFillMemory(), the user should ensure that memory range specified does not overlap into the UUTDiagsBaseAddress memory area reserved for execution of the machine code routines. Also, the user should ensure that memory has been initialized sufficiently to allow the machine code routines to run properly. In both cases, the function may fail to return normally (i.e. unless forced using ai\_mStopTest()).

## **RETURN VALUE**

On success, ai mFillMemory() returns 0. On error, it will return one of the following values:

## ERRORS

| AI_INVALID_PARAM           | Invalid parameter                                    |

|----------------------------|------------------------------------------------------|

| AI_VCC_NOT_FOUND           | Target not powered up                                |

| AI_MAX_UNCORES_EXCEEDED    | Scan chain init: maximum possible Uncores exceeded   |

| AI_INVALID_CORE_IDCODE_DET | Scan chain init: an invalid Core IDCODE was detected |

|                            | © 2021 ASSET InterTech, Inc.                         |

| AI_INVALID_UNCORE_IDCODE_DET   | Scan chain init: an invalid Uncore IDCODE was detected                 |

|--------------------------------|------------------------------------------------------------------------|

| AI_ERR_TAP_OWNERSHIP           | Scan chain init: error getting ownership of the TAP                    |

| AI_CFG_JTAG                    | Scan chain init: error configuring JTAG                                |

| AI_DBG_MODE_FILL_MEM           | Error during execution of fill memory operation                        |

| AI_FILL_MEM_HALTED_USR         | Execution of fill memory operation interrupted by user                 |

| AI_FILL_MEM_HALTED_UNKNWN_SRC  | Execution of fill memory operation interrupted by unknown source       |

| AI_SA_GREATER_THAN_EA          | Start address cannot be greater than end address                       |

| AI_NO_EXEC_HALT_STATE          | Target core in HALT state – unable to execute user diagnostic          |

| AI_NO_EXEC_WAIT_FOR_SIPI_STATE | Target core in WAIT FOR SIPI state – unable to execute user diagnostic |

| AI_NO_EXEC_SHUTDOWN_STATE      | Target core in SHUTDOWN state – unable to execute user diagnostic      |

| AI_ERR_PCT_INT_IOCTL           | Error reported from <code>IOCTL()</code> function                      |

| AI_RESTORE_JTAG_CFG_DEFAULT    | Error restoring JTAG configuration settings to default                 |

#### FILES

Pentcode.hex - machine code routines collection. Can be installed to any directory. UUTDiagsHexFile from ai\_mConfig() provides the ITP driver library with a pointer to the machine code file.

#### SEE ALSO

ai\_mCheckMemory

ai\_mStopTest

#### ai\_mFXRSTOR

NAME

#### ai mFXRSTOR

Execute the Pentium FXRSTOR instruction.

#### **SYNOPSIS**

#include <itp\_driver.h>

int ai mFXRSTOR (int mHandle, uint64 t BaseAddress);

#### DESCRIPTION